10.1. PSPICE как статический логический анализатор

10.1. PSPICE как статический логический анализатор

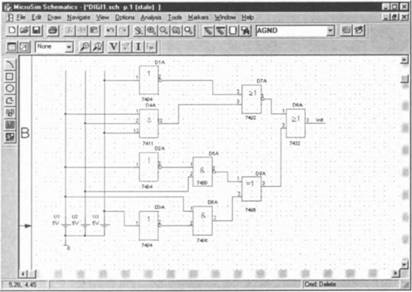

Шаг 1 Начертите в редакторе SCHEMATICS схему, изображенную на рис. 10.1. Необходимые компоненты вы найдете в библиотеке EVAL.slb. Редактор для установления метки (out) можно открыть, дважды щелкнув мышью по соответствующему участку проводки. Сохраните готовую схему в папке Projects под именем DIGI1.sch.

Рис. 10.1. Логическая схема с различными компонентами цифровой техники

Вы можете на выбор настроить источники постоянного напряжения U1, U2 и U3 на ТТЛ-уровень низкого сигнала (L=0 В) или высокого сигнала (H=5 В). Тогда программа PSPICE проведет логический анализ этих напряжений.

Шаг 2 Установите все источники напряжения U1, U2 и U3 на уровень высокого сигнала, то есть на 5 В. Откройте окно Analysis Setup и снимите установленные в нем флажки, чтобы деактивизировать все без исключения анализы. Затем с помощью кнопки желтого цвета запустите моделирование. Сейчас программа PSPICE производит такие расчеты, которые она выполняет в процессе любого моделирования, в том числе расчеты логических состояний. Однако PSPICE не показывает результаты их вычисления автоматически. Чтобы вызвать на экран индикаторы логических состояний, нужно специально их запросить.

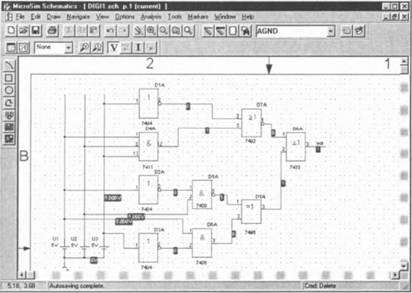

Шаг 3 Щелкните по кнопке с изображением большой буквы V, с которой вы познакомились в ходе второго урока (с ее помощью вы вызывали индикаторы потенциалов в рабочих точках) — см. рецепт 2 в главе 2. Теперь программа PSPICE показывает вам логические состояния (рис. 10.2).

Рис. 10.2. Цифровая схема с индикаторами логических состояний

Шаг 4 Попробуйте другие комбинации входных напряжений и путем моделирования установите соответствующие им логические состояния.

Программа PSPICE проделывает это просто замечательно, но и вы, проявив немного терпения, сделали бы не хуже. Логический анализ, проводимый компьютером, только тогда сможет произвести на вас должное впечатление, когда вы используете в своей схеме одновременно и цифровые, и аналоговые компоненты.

Допустим, нам нужно дополнить схему, изображенную на рис. 10.1, таким образом, чтобы при формировании сигнала высокого уровня (лог. 1) на выходе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (X-OR) загоралась красная лампочка (5 В/200 Ом). Сопротивление 200 Ом для выхода ТТЛ-схемы — довольно внушительная нагрузка. Необходимо исследовать, сможет ли элемент X-OR подавать такое напряжение, которого будет достаточно, чтобы следующий за ним логический элемент ИЛИ D15A воспринял его как сигнал высокого уровня (лог. 1). В ТТЛ-технике для этого требуется напряжение как минимум 2 В.

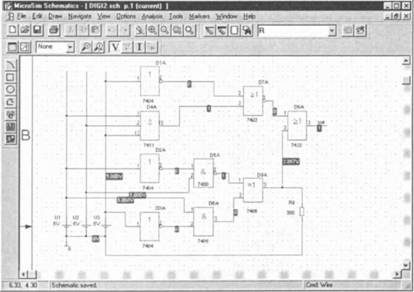

Шаг 5 Дополните свою схему, установив в ней резистор сопротивлением 200 Ом на выходе логического элемента X-OR (рис. 10.3), и сохраните ее под именем DIGI2.sch. Затем проведите моделирование этой схемы, установив такую комбинацию входных напряжений, которая позволила бы ожидать сигнала высокого уровня (лог. 1) на выходе элемента X-OR. После щелчка по кнопке с изображением большой буквы V чертеж должен приобрести такой же вид, как на рис. 10.3.

Рис. 10.3. Цифровая схема с дополнительным резистором

Взглянув на рис. 10.3, вы можете заметить, каким интересным качеством обладает PSPICE при одновременном моделировании аналоговых (резисторы, конденсаторы, транзисторы, источники напряжения аналогового сигнала и т.п.) и цифровых (логические элементы) компонентов. В тех местах, где узловые пункты связывают исключительно цифровые компоненты, моделирование выявляет цифровые состояния (1 или 0). Там, где на узле находится хотя бы один аналоговый компонент, выдаются значения напряжения. Видно, что напряжение на выходе логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (X-OR) как раз немногим выше двух вольт. Значит, этот резистор может быть подключен напрямую, то есть без дополнительных формирователей.

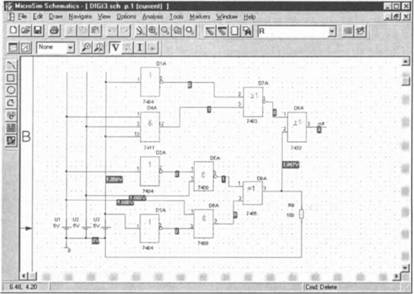

Шаг 6 Уменьшите сопротивление резистора до 180 Ом, сохраните схему под именем DIGI3.sch и с помощью моделирования убедитесь, что при таком сопротивлении напряжение уже не преодолевает TTЛ-границу равную 2 В. Напряжения, имеющие значения от 0.8 до 2 В, в технике выполнения ИС в базисе ТТЛ считаются неопределенными состояниями. Обратите внимание: неопределенное состояние логического элемента X-OR приводит к тому, что выход, где установлена метка out, также принимает неопределенное состояние, которое программа PSPICE обозначает как X (рис. 10.4).

Рис. 10.4. Цифровая схема, где выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ D18A перегружен и не может передать сигнал достаточно высокого уровня

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКЧитайте также

Статический вес

Статический вес Определение страниц, получающих недостаточный статический вес. Часть важных страниц может недополучать статический вес. Вместо этого наибольший вес может переходить к непродвигаемым и техническим страницам. Чтобы решить эту проблему, необходимо:?

Объекты имеют статический тип

Объекты имеют статический тип Один из выводов, который можно сделать из трех требований QueryInterfасе , состоит в том, что множество интерфейсов, поддерживаемых объектом, не может изменяться во времени. Спецификация СОМ четко требует, чтобы этот вывод был верен для всех

Логический размер изображения

Логический размер изображения Логический размер изображения, измеряемый в сантиметрах, миллиметрах или других единицах длины, является относительным. Изображение может быть легко увеличено или уменьшено на мониторе, выведено на печать с бульшим или меньшим

17.5.3. Статический вызов виртуальной функции

17.5.3. Статический вызов виртуальной функции Вызывая виртуальную функцию с помощью оператора разрешения области видимости класса, мы отменяем механизм виртуализации и разрешаем вызов статически, на этапе компиляции. Предположим, что мы определили виртуальную функцию isA()

Логический контекст

Логический контекст Простой способ рассматривать транзакцию между START TRANSACTION и COMMIT или ROLLBACK - это смотреть на нее как на серию клиентских операций и взаимодействий клиента и сервера, которые точно отображают задачу. Это очень полезная модель для понимания того, как

Анализатор статистики IBAnalyst

Анализатор статистики IBAnalyst IBAnalyst- это инструмент для анализа статистики баз данных InterBase или Firebird, поиска проблем в производительности базы данных, сопровождении, или работы приложений.IBAnalyst решает две важные задачи:* визуализирует статистику базы данных и сообщает об

20.1. Анализатор использования диска

20.1. Анализатор использования диска Вместо консольной (текстовой) утилиты df (см. разд. 21.6.1) для анализа использования диска можно использовать графическую программу Приложения | Стандартные, Анализатор использования дисков (рис. 20.1). Программа эта удобнее не только тем,

Логический тип

Логический тип Значения логического типа boolean занимают 1 байт и принимают одно из двух значений, задаваемых предопределенными константами True (истина) и False (ложь).Для логического типа определены статические методы: boolean.Parse(s) - функция, конвертирующая строковое

ТЕМА НОМЕРА: Логический блок

ТЕМА НОМЕРА: Логический блок Автор: Сергей ВильяновИнтервью с Дмитрием Дёминым, менеджером по развитию канала продаж расходных материалов российского офиса компании Hewlett-PackardДмитрий, давайте начнем с вопроса, который мне все равно пришлось бы вам задать в ходе беседы.

4.1.3. Что такое раздел или логический диск

4.1.3. Что такое раздел или логический диск Накопителям данных в Windows принято присваивать буквы латинского алфавита. Такая традиция пришла в Windows из DOS. Буквы A: и B: зарезервированы для дисководов на гибком диске (неужели у вас они еще есть?). Буква С: — это системный диск, с

Статический тип, динамический тип

Статический тип, динамический тип Название последнего свойства предполагает различение "статического типа" и "динамического типа". Тип, который используется при объявлении некоторого элемента, является статическим типом соответствующей ссылки. Если во время выполнения

Статический механизм

Статический механизм Устранить последнее неясности в понимании закрепленного объявления поможет следующее замечание: это чисто статический механизм, не предполагающий никаких изменений объектов в период выполнения. Все ограничения могут быть проверены в период