Усилители на полевых транзисторах

Усилители на полевых транзисторах

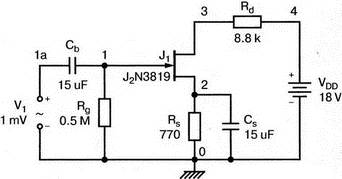

В схеме усилителя на полевом транзисторе, приведенной на рис. 11.7, использовалась встроенная модель транзистора. Как говорилось в этом примере, строки, описывающие такое устройство, могли бы иметь вид:

JFET 3 1 2 JM

.MODEL JM NJF (RD=10 RS=10 VTO=3V BETA=0.2m)

Эти строки вводят универсальный встроенный полевой транзистор JFET, для которого мы выбрали имя JM. Если мы создаем эту схему с помощью Capture, мы не можем просто выбрать компонент JFET; вместо этого мы должны выбрать один из доступных компонентов с конкретным именем. Затем можно изменить параметры модели так, чтобы она удовлетворяла нашим требованиям.

Начните новый проект с именем Jfetampl и введите схему, показанную в рис. 11.7, используя компоненты VAC (для Vi), C (для Сb и Cs), R (для Rg, Rd и Rs), J2N3819 (для полевого транзистора) и VDC (для VDD). Задайте значения компонентов, которые использовались ранее. Схема, которую вы должны получить, показана на рис. 15.26. Полевой транзистор, используемый на рис. 11.7, описывается в PSpice командой

.MODEL JM NJF (RD=10 RS = 10 VTO=-3V BETA=0.2m)

Рис. 15.26. Усилитель на полевом транзисторе

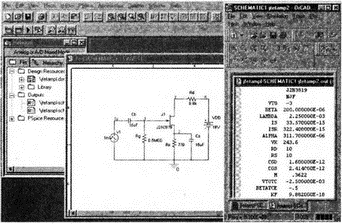

Отредактируем модель конкретного транзистора J2N3819 так, чтобы она соответствовала этой команде. Выберите JFET, щелкнув на его символе, затем выберите Edit, PSpice Model. При этом на экране появится окно OrCAD Model Editor, в котором могут быть сделаны изменения. Задайте «Beta=0.2 m», «Rd=10» и «Rs=10», как показано на рис. 15.27. Сохраните эти изменения и закройте окно редактора модели.

Рис. 15.27. Изменение параметров транзистора JFET в программе Model Editor

Сохраните схему и подготовьте новую конфигурацию моделирования на PSpice с именем jfetamps. Анализ должен быть проведен при линейной вариации частоты от 4900 до 5100 Гц, используя 201 точку.

Выполните анализ, и в Probe проверьте значения следующих величин при f=5 кГц: I(Rd)=0,876 мкА; V(1)=1 мВ; V(3)=7,73 мВ и V(2)=1,8 мкВ. Отметим, что различные напряжения могут также быть отображены при использовании записей типа V(Cb:2), V(Rd:1), V(Rs:1) и т.п.

Вообще предпочтительно пронумеровать предварительно узлы и обращаться затем к напряжениям с номерами узлов. Таким образом, в этом примере V(3) представляет собой напряжение на стоке JFET относительно земли. Нумерация узлов задается также командой псевдонимов выходного файла:

J_J J1(d=3 g=1 s=2)

что еще проще понять. Если вы забудете перенумеровать узлы, вы будете иметь дело с громоздкими обозначениями автоматической нумерации типа N00034. В выходном файле на рис. 15.28 показан список измененных параметров J2N3819. Значение VТО=–3 не было изменено, но Beta, Rd и Rs были заменены приведенными значениями. Выходной файл, приведенный на рис. 15.29, показывает компоненты схемы, значения параметров и напряжения смещения для VDD=18 В. Выходной файл может содержать следующие инструкции:

WARNING-Unable to find index file (JFETAMPL.ind) for library file JFETAM + PL.lib

WARNING-Making new index file (JFETAMPL.ind) for library file JFETAMPL.lib Index has 1 entries from 1 file(s).

(ПРЕДУПРЕЖДЕНИЕ — Невозможно найти индексный файл (JFETAMPL.IND) для библиотечного файла JFETAM + PL.LIB

ПРЕДУПРЕЖДЕНИЕ — Создайте новый индексный файл (JFETAMPL.IND) для библиотечного файла JFETAMPL.LIB Индекс имеет 1 вход из 1 файла(ов).)

Рис. 15.28. Схема JFET и изменение выходного файла

**** 10/03/99 14:20:08 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profiles jfetamps

*Libraries:

* Local Libraries :

.LIB ".jfetampl.lib"

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.AC LIN 201 4900Hz 5100Hz

.PROBE

*Netlist File:

.INC "jfetampl-SCHEMATIC1.net"

*Alias Files

**** INCLUDING jfetampl-SCHEMATIC1.net ****

* source JFETAMPL

V_VDD 4 0 18V

R_Rs 2 0 770

R_Rg 1 0 0.5MEG

R_Rd 3 4 8.8k

С_Cs 2 0 15uF

С_Cb 1A 1 15uF

J_J1 3 1 2 J2N3819

V_V1 1A 0 DC 0V AC 1mV 0

**** RESUMING jfetampl-SCHEMATIC1-jfetamps.sim.cir ****

.INC "jfetampl-SCHEMATIC1.als"

**** INCLUDING jfetampl-SCHEMATIC1.als ****

.ALIASES

V_VDD VDD(+=4 -=0 )

R_Rs Rs(1=2 2=0 )

R_Rg Rg(1=1 2=0 )

R_Rd Rd(1=3 2=4 )

C_Cs Cs(1=2 2=0 )

C_Cb Cb(1=1A 2=1 )

J_J1 J1(d=3 g=1 s=2 )

V_V1 V1(+=1A -=0 )

.ENDALIASES

.END

**** Junction FET MODEL PARAMETERS

J2N3839

NJF

VTO -3

BETA 200.000000E-06

LAMBDA 2.250000E-03

IS 33.570000E-15

ISR 322.400000E-15

ALPHA 311.700000Е-06

VK 243.6

RD 10

RS 10

BETATCE -.5

KF 9.882000E-18

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 605.8E-09 ( 2) .7719 ( 3) 9.1779 ( 4) 18.0000

( 1A) 0.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

V_VDD -1.003E-03

V_V1 0.000E+00

TOTAL POWER DISSIPATION 1.80E-02 WATTS

Рис. 15.29. Выходной файл усилителя на JFET-транзисторе

Эти предупреждения служат напоминанием, что до выполнения анализа библиотечный файл jfetampl.lib отсутствует. Он будет создан после выполнения анализа наряду с файлом jfetampl.ind. Новый библиотечный файл находится в вашем каталоге SPICE и содержит исходные данные, показанные на рис. 15.27. Листинг идентичен существующему в eval.lib, за исключением параметров Beta, Rd и Rs, которые мы изменили. Новая модель называется локальной моделью и доступна для использования только со схемой jfetampl.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

Двухкаскадные усилители

Двухкаскадные усилители При использовании PSpice расчет двухкаскадных усилителей очень прост, и результат получается быстрее, чем при расчете с использованием формул, который утомителен и требует сосредоточенности, чтобы не допустить ошибки. Понимая основные принципы

Частотная характеристика усилителя на полевых транзисторах

Частотная характеристика усилителя на полевых транзисторах При использовании усилителя на полевом транзисторе в широком диапазоне частот необходимо учитывать внутренние емкости транзисторов. На рис. 3.33 приведена модель усилителя с общим истоком (ОИ), включающая

5. Операционные усилители

5. Операционные усилители Операционный усилитель (ОУ), или op amp, представляет собой интегральную схему, широко используемую в электронике. Реальная схема усилителя сложна и нет необходимости отражать все ее свойства в нашей модели. Мы начнем с модели идеального ОУ,

Дифференциальные усилители

Дифференциальные усилители Дифференциальный усилитель используется в качестве первого каскада ОУ. В простейшем случае он напоминает схему на рис. 9.22. Для анализа мы используем встроенную модель для npn-транзистора, применив согласованную пару для Q1 и Q2, выбрав Rs1=Rs2=1 кОм и

Усилители с общим эмиттером

Усилители с общим эмиттером Простая схема каскада с ОЭ показана на рис. 10.5. Входной контур получен путем преобразования более сложной цепи с помощью теоремы Тевенина. Мы проводим анализ при частоте 5 кГц, при которой конденсаторы могут рассматриваться просто как короткое

Триггер на биполярных транзисторах

Триггер на биполярных транзисторах Рис. 10.22. Триггер на биполярных транзисторахТриггер, использующий транзисторы BJT npn-типа, показан на рис. 10.22. Для обеспечения правильной работы в этом мультивибраторе с двумя устойчивыми состояниями один транзистор должен находиться в

Мультивибратор с эмиттерными связями на биполярных транзисторах

Мультивибратор с эмиттерными связями на биполярных транзисторах На рис. 10.29 показан мультивибратор с эмиттерными связями, использующий стандартные компоненты. Его подробный анализ приведен в книге Millman, Taub, Pulse, Digital, and Switching Waveforms. При анализе принимается, что Q1

Выходные характеристики полевых транзисторов

Выходные характеристики полевых транзисторов Демонстрационная версия PSpice содержит модели для двух типов n-канальных полевых транзисторов (JFET) в библиотеке EVAL.LIB. Получим необходимый набор выходных характеристик для транзистора J2N3819. Входной файл для анализа схемы рис.

Входные характеристики усилителя на полевых транзисторах

Входные характеристики усилителя на полевых транзисторах При получении входных характеристик величина VGS используется во внешнем цикле команды .DC в качестве основной переменной, откладываемой по оси X. Значения VDD изменяются от от 2 до 10 В с шагом в 4 В, создавая три

Токи смещения полевых транзисторов

Токи смещения полевых транзисторов Схема с автоматическим смещением приведена на рис. 11.4. Во встроенной модели для n-канального JFET значения, заданные по умолчанию для ряда параметров, изменены. Новые значения показаны в следующем входном файле: n-Channel JFET Bias CircuitVDD 4 0 18VRG 1 0

Усилители на MOSFET

Усилители на MOSFET Усилитель мощности, использующий IRF150, показан на рис. 11.14. Так как используется режим с большими токами истока и стока, значения Rd и Rs составляют 2 и 0,5 Ом соответственно. Резисторы R1 и R2 образуют делитель напряжения, обеспечивающий значение VGS=4,7 В. При этом

Изучение схем с общим эмиттером на биполярных транзисторах

Изучение схем с общим эмиттером на биполярных транзисторах Для изучения цепей смещения в главе 10 была использована схема на рис. 10.7. Соберите эту схему в Capture, создав новый проект Bjtcase. Напомним, что необходимо трижды повернуть резисторы, чтобы первый полюс каждого

Характеристики полевых транзисторов

Характеристики полевых транзисторов Демонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис.

Усилители на полевых транзисторах

Усилители на полевых транзисторах В схеме усилителя на полевом транзисторе, приведенной на рис. 11.7, использовалась встроенная модель транзистора. Как говорилось в этом примере, строки, описывающие такое устройство, могли бы иметь вид:JFET 3 1 2 JM.MODEL JM NJF (RD=10 RS=10 VTO=3V BETA=0.2m)Эти

16. Операционные усилители в Capture

16. Операционные усилители в Capture Идеальный операционный усилитель был представлен в главе 5 (рис. 5.1). Использование этой модели в Capture почти тривиально, но мы повторим задачу, показанную на рис. 5.4, для введения в более сложные