Характеристики полевых транзисторов

Характеристики полевых транзисторов

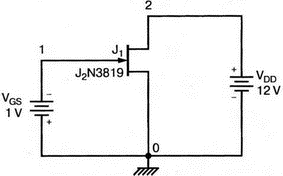

Демонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис. 15.22). Номинальные значения для VGS и VDD показаны на рисунке. Определите опции моделирования в Simulation Profile, используя имя jfetchs. Внутренний цикл вариации использует значения источника напряжения VDD от 0 до 12 В с шагом в 0,2 В. Внешний цикл определяется изменением напряжения VGS от 0 до 4 В с шагом в 1 В.

Рис. 15.22. Схема смещения для n-канального полевого транзистора

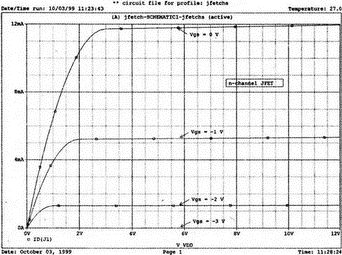

Выполните моделирование и получите в Probe график ID(J1). Вы должны получить семейство кривых с параметром VGS, приведенных на рис. 15.23. Кривые показывают, что наибольшие токи соответствуют VGS=0. Ниже расположена кривая с параметром VGS=–1 В и так далее. Напряжением отсечки является VGS=–3 В.

Рис. 15.23. Ток стока в n-канальном полевом транзисторе

Выходной файл включает параметры модели J2N3S19: пороговое напряжение (отсечки) VTO=-3 В, коэффициент передачи BETA и другие. Они отражены на рис. 15.24. В приложении D приведены все параметры модели для J (JFET).

**** 10/03/99 11:45:33 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: jfetchs

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.DC LIN V VDD 0V 12V 0.2V

+ LIN V_VGS 0V 4V 1V

.PROBE

*Netlist File:

.INC "jfetch-SCHEMATIC1.net"

*Alias File:

**** INCLUDING jfetch-SCHEMATIC1.net ****

* source JFETCH

J_J1 2 1 0 J2N3819

V_VDD 2 0 12V

V_VGS 0 1 1V

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir

**** .INC "jfetch-SCHEMATIC1.als"

**** INCLUDING jfetch-SCHEMATIC1.als ****

.ALIASES

J_J1 J1(d=2 g=1 s=0 )

V_VDD VDD(+=2 -=0 )

V_VGS VGS(+=0 -=1 )

_ _(1=1)

_ _(2=2)

.ENDALIASES

.END

**** Junction FET MODEL PARAMETERS

J2N3819

NJF

VTO -3

BETA 1.304000E-03

LAMBDA 2.250000E-03

IS 33.570000E-15

ISR 322.400000E-15

ALPHA 311.700000E-06

VK 243.6

RD 1

RS 1

CGD 1.600000E-12

CGS 2.414000E-12

M .3622

VTOTC -2.500000E-03

BETATCE -.5

KF 9.882000E-18

Рис. 15.24. Выходной файл для n-канального полевого транзистора

Хотя предыдущие выпуски программного обеспечения от MicroSim использовали для создания рисунков программу Schematics вместо Capture, автоматически формируя команду .ОР в схемном файле, используемая в книге версия Capture этого не делает. Следовательно, значения параметров смещения не выводятся в выходном файле. Чтобы получить эти значения, отредактируете параметры настройки моделирования и запросите анализ параметров смещения путем проверки с опцией .OP. Выходной файл при таком запуске показан на рис. 15.25. Информация, дублирующая информацию предыдущего выходного файла, из него удалена. Убедитесь, что выходной файл соответствует графику, показывая VDD=12 В, VGS=–1 В, IDD=5,328 мА.

**** 10/03/99 12:27:36 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: jfetchs

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.OP

.PROBE

*Netlist File:

.INC "jfetch-SCHEMATIC1.net"

*Alias File:

**** INCLUDING jfetch-SCHEMATIC1.net ****

* source JFETCH

J_J1 2 10 J2N3819

V_VDD 2 0 12V

V_VGS 0 1 1V

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir ****

.INC "jfetch-SCHEMATIC1.als"

**** INCLUDING jfetch-SCHEMATIC1.als ****

.ALIASES

J_J1 J1(d=2 g=1 s=0 )

V_VDD VDD(+=2 -=0)

V_VGS VGS(+=0 -=1 )

_ _(1=1)

_ _(2=2)

.ENDALIASES

**** RESUMING jfetch-SCHEMATIC1-jfetchs.sim.cir ****

.END

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) -1.0000 ( 2) 12.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

V_VDD -5.328E-03

V_VGS -1.321E-12

TOTAL POWER DISSIPATION 6.39E-02 WATTS

**** JFETS

NAME J_J1

MODEL J2N3819

ID 5.33E-03

VGS -1.00E+00

VDS 1.20E+01

GM 5.34E-03

GDS 1.17E-05

CGS 1.83E-12

CGD 6.15E-13

Рис. 15.25. Выходной файл, использующий опцию .OР

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

1.3 Характеристики TCP/IP

1.3 Характеристики TCP/IP TCP/IP обладает уникальными характеристиками, которые обеспечивают долговечность этих протоколов. Архитектура TCP/IP позволяет объединять сетевые кластеры, формируя то, что называется "интернетом". Для пользователя интернет выглядит как одна большая

Малосигнальная модель с h -параметрами для биполярных транзисторов

Малосигнальная модель с h-параметрами для биполярных транзисторов Точной моделью для биполярных транзисторов, широко используемой при анализе на малых сигналах, является модель в h-параметрах, показанная на рис. 3.5. Эта модель с соответствующими значениями используется

Частотная характеристика усилителя на полевых транзисторах

Частотная характеристика усилителя на полевых транзисторах При использовании усилителя на полевом транзисторе в широком диапазоне частот необходимо учитывать внутренние емкости транзисторов. На рис. 3.33 приведена модель усилителя с общим истоком (ОИ), включающая

Чувствительность биполярных транзисторов из библиотеки PSpice

Чувствительность биполярных транзисторов из библиотеки PSpice Когда при анализе чувствительности используется модель биполярного транзистора из библиотеки PSpice, чувствительность выходной переменной к изменениям в значениях параметров транзистора задана также в

Выходные характеристики

Выходные характеристики Схема для получения выходных характеристик (рис. 10.1) содержит источник постоянного напряжения VCC с варьируемым выходным напряжением и источник постоянного тока IВ с варьируемым током. Транзистор обозначен как Q1. При использовании встроенной

Входные характеристики

Входные характеристики Чтобы получить входные характеристики, можно использовать схему, показанную на рис. 10.3. Источник тока IВВ превращается в неидеальный при включении параллельно его выходу резистора Rs. Входной файл:BJT Input CharacteristicsIBB 0 1 100uARs 1 0 1000kRL 2 3 0.01Q1 2 1 0 BJTVCC 3 0 10V.MODEL BJT

Выходные характеристики полевых транзисторов

Выходные характеристики полевых транзисторов Демонстрационная версия PSpice содержит модели для двух типов n-канальных полевых транзисторов (JFET) в библиотеке EVAL.LIB. Получим необходимый набор выходных характеристик для транзистора J2N3819. Входной файл для анализа схемы рис.

Входные характеристики усилителя на полевых транзисторах

Входные характеристики усилителя на полевых транзисторах При получении входных характеристик величина VGS используется во внешнем цикле команды .DC в качестве основной переменной, откладываемой по оси X. Значения VDD изменяются от от 2 до 10 В с шагом в 4 В, создавая три

Токи смещения полевых транзисторов

Токи смещения полевых транзисторов Схема с автоматическим смещением приведена на рис. 11.4. Во встроенной модели для n-канального JFET значения, заданные по умолчанию для ряда параметров, изменены. Новые значения показаны в следующем входном файле: n-Channel JFET Bias CircuitVDD 4 0 18VRG 1 0

Усилители на полевых транзисторах

Усилители на полевых транзисторах Можно преобразовать схему смещения, показанную на рис. 11.4, в усилитель напряжения, добавив два конденсатора и источник переменного напряжения (рис. 11.7). Приведенный ниже входной файл предназначен для анализа на переменном токе при f=5

Выходные характеристики

Выходные характеристики Чтобы получить выходные характеристики, используем схему, показанную на рис. 11.11. Входной файл для нее:n-Channel MOSFET Output CharacteristicsVDD 2 0 12VVGS 1 0 0VMFET 2 10 0 IRF150; сток, исток, затвор и подложка.DC VDD 0 12V 0.8V VGS 0 8V 1V.LIB EVAL.LIB.PROBE.END Рис. 11.11. Схема для снятия характеристик

Входные характеристики

Входные характеристики Для входных характеристик несколько значений VDD будут использоваться, как показано в следующем файле:Input Characteristic for MOSFETVGS 1 0 0VVDD 2 0 10VMOS 2 10 0 IRF150.DC VGS 0 8V 0.1V VDD 2V 10V 4V .PROBE.LIB EVAL.LIB.ENDПолученный в результате график показан на рис. 11.13. Из него видно, что

Усилители на полевых транзисторах

Усилители на полевых транзисторах В схеме усилителя на полевом транзисторе, приведенной на рис. 11.7, использовалась встроенная модель транзистора. Как говорилось в этом примере, строки, описывающие такое устройство, могли бы иметь вид:JFET 3 1 2 JM.MODEL JM NJF (RD=10 RS=10 VTO=3V BETA=0.2m)Эти

Характеристики.

Характеристики. PGPfone позволяет "говорить на ухо" по телефону, даже если это ухо расположено в тысячах миль от вас.PGPfone (Pretty Good Privacy Phone) — это программный продукт, который превращает ваш персональный компьютер или ноутбук в защищенный телефон. Для того, чтобы предоставить

Характеристики PGPfone 2.0

Характеристики PGPfone 2.0 • Выбор технологии сжатия речевого потока (GSM, GSM Lite and ADPCM) с возможностью динамической ее смены без разрыва связи. Это позволяет достичь оптимального качества звука.• Возможность защищенного обмена файлами.• Телефонная записная