Токи смещения полевых транзисторов

Токи смещения полевых транзисторов

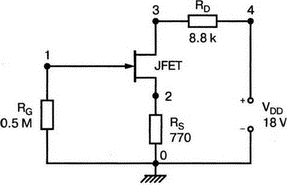

Схема с автоматическим смещением приведена на рис. 11.4. Во встроенной модели для n-канального JFET значения, заданные по умолчанию для ряда параметров, изменены. Новые значения показаны в следующем входном файле:

n-Channel JFET Bias Circuit

VDD 4 0 18V

RG 1 0 0.5MEG

RS 2 0 770

RD 4 3 8.8k

JFET 3 1 2 JM

.MODEL JM NJF(RD=10 RS=10 VTO=-3 BETA=0.2m)

.DC VDD 18V 18V 18V

.OP

.OPT nopage

.PRINT DC I(RD) I(RS) I(RG) .END

Рис. 11.4. Схема с автоматическим смещением транзистора JFET

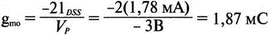

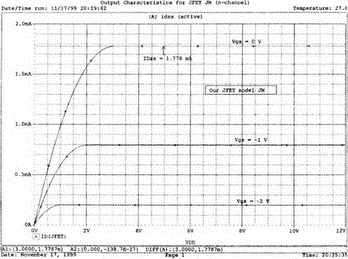

Выходной файл приведен на рис. 11.5. Чтобы посмотреть, совпадают ли результаты стандартного схемотехнического расчета и анализа на PSpice, необходимо найти значение IDSS. Выполните анализ, подобный показанному на рис. 11.2, и убедитесь, что для этого JFET IDSS=1,78 мА. Сравните ваши результаты с рис. 11.6. Воспользовавшись этим значением, найдем

**** 07/29/99 11:29:21 *********** Evaluation PSpice (Nov 1998) **************

n-Channel JFET Bias Circuit

VDD 4 0 18V

RG 1 0 0.5MEG

RS 2 0 770

RD 4 3 8.8k

JFET 3 1 2 JM

.MODEL JM NJF(RD=10 RS=10 VTO=-3 BETA=0.2m)

.DC VDD 18V 18V 18V

.OP

.opt nopage

.PRINT DC I(RD) I(RS) I(RG)

.END

**** Junction FET MODEL PARAMETERS

JM

NJF

VTO -3

BETA 200.000000E-06

RD 10

RS 10

**** DC TRANSFER CURVES TEMPERATURE = 27.000 DEG С

VDD I(RD) I(RS) I(RG)

1.800E+01 9.915E-04 9.915E-04 1.006E-11

**** SMALL SIGNAL BIAS SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 5.029E-06 ( 2) .7635 ( 3) 9.2744 ( 4) 18.0000

VOLTAGE SOURCE CURRENTS

NAME CURRENT

VDD -9.915E-04

TOTAL POWER DISSIPATION 1.78E-02 WATTS

**** JFETS

NAME JFET

MODEL JM

ID 9.92E-04

VGS -7.63E-01

VDS 8.51E+00

GM 8.91E-04

GDS 0.00E+00

CGS 0.00Е+00

CGD 0.00Е+00

Рис. 11.5. Выходной файл с результатами анализа схемы на рис. 11.4

Рис. 11.6 Выходные характеристики схемы на рис. 11.4

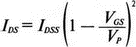

Используем теперь значение IDSS, полученное в PSpice, чтобы найти VGSS. В следующем уравнении IDSS представляет собой ток стока при насыщении:

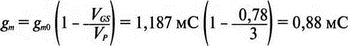

Откуда при IDS=0,992 мА, IDSS=-1,78 мА и VP=3 В после преобразований получим VGS=0,78 В и затем

Значения VGS и gm согласуются с показанными на рис. 11.5.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

6.14.3 Поле смещения фрагмента

6.14.3 Поле смещения фрагмента Блок фрагментации (fragment block) — это 8-октетная порция данных. Число в поле смещения фрагмента (Fragment Offset) указывает величину смещения данного фрагмента (относительно начала датаграммы) в единицах блоков фрагментирования. Это поле имеет длину 13

Модели, предназначенные для расчета смещения

Модели, предназначенные для расчета смещения Чтобы использовать анализ на PSpice, мы предлагаем вам разработать подходящую модель для BJT. Она позволит вам находить статические значения напряжений и токов в схеме смещения. На рис. 3.2 показана такая модель наряду с другими

Расчет смещения для германиевого транзистора

Расчет смещения для германиевого транзистора В качестве другого примера на рис. 3.3 показана схема смещения для германиевого pnp-транзистора с hFE=60 и VBE=-0,2 В. Значения параметров элементов схемы: RF=50 кОм; RE=50 Ом; RC=1 кОм и VCC=-12 В. Заменив транзистор моделью PSpice, мы получим схему

Малосигнальная модель с h -параметрами для биполярных транзисторов

Малосигнальная модель с h-параметрами для биполярных транзисторов Точной моделью для биполярных транзисторов, широко используемой при анализе на малых сигналах, является модель в h-параметрах, показанная на рис. 3.5. Эта модель с соответствующими значениями используется

Частотная характеристика усилителя на полевых транзисторах

Частотная характеристика усилителя на полевых транзисторах При использовании усилителя на полевом транзисторе в широком диапазоне частот необходимо учитывать внутренние емкости транзисторов. На рис. 3.33 приведена модель усилителя с общим истоком (ОИ), включающая

Чувствительность по току смещения

Чувствительность по току смещения На рис. 3.41 представлена наша модель для схемы смещения для биполярного транзистора. В этом примере транзистор имеет VBE=0,7 В и hFE= 80. Выходным напряжением считается напряжение коллектор-эмиттер V(3,2). Это напряжение будет предметом анализа

Чувствительность биполярных транзисторов из библиотеки PSpice

Чувствительность биполярных транзисторов из библиотеки PSpice Когда при анализе чувствительности используется модель биполярного транзистора из библиотеки PSpice, чувствительность выходной переменной к изменениям в значениях параметров транзистора задана также в

Анализ цепей смещения

Анализ цепей смещения Схема с более устойчивой точкой покоя, чем в предыдущем случае, показана на рис. 10.7. Она называется схемой с эмиттерным или автоматическим смещением. Входной файл:Biasing Case StudyVCC 2 0 12VR1 2 1 40kR2 1 0 3.3kRC 2 3 4.7kRE 4 0 220Q1 3 1 4 Q2N2222.LIB EVAL.LIB; команда вызывает библиотечный

Выходные характеристики полевых транзисторов

Выходные характеристики полевых транзисторов Демонстрационная версия PSpice содержит модели для двух типов n-канальных полевых транзисторов (JFET) в библиотеке EVAL.LIB. Получим необходимый набор выходных характеристик для транзистора J2N3819. Входной файл для анализа схемы рис.

Входные характеристики усилителя на полевых транзисторах

Входные характеристики усилителя на полевых транзисторах При получении входных характеристик величина VGS используется во внешнем цикле команды .DC в качестве основной переменной, откладываемой по оси X. Значения VDD изменяются от от 2 до 10 В с шагом в 4 В, создавая три

Усилители на полевых транзисторах

Усилители на полевых транзисторах Можно преобразовать схему смещения, показанную на рис. 11.4, в усилитель напряжения, добавив два конденсатора и источник переменного напряжения (рис. 11.7). Приведенный ниже входной файл предназначен для анализа на переменном токе при f=5

Характеристики полевых транзисторов

Характеристики полевых транзисторов Демонстрационная версия OrCAD имеет компоненты J2N3819 и J2N4393 в качестве моделей для полевых n-канальных транзисторов (JFET). Чтобы получить семейство выходных характеристик, создайте новый проект с именем Jfetch. Используем простую схему (рис.

Усилители на полевых транзисторах

Усилители на полевых транзисторах В схеме усилителя на полевом транзисторе, приведенной на рис. 11.7, использовалась встроенная модель транзистора. Как говорилось в этом примере, строки, описывающие такое устройство, могли бы иметь вид:JFET 3 1 2 JM.MODEL JM NJF (RD=10 RS=10 VTO=3V BETA=0.2m)Эти

2.1. Токи и напряжения в цепях постоянного тока

2.1. Токи и напряжения в цепях постоянного тока Все напряжения, которые вычисляет PSPICE, являются напряжениями между отдельными точками электросхемы и одной опорной точкой, местоположение которой определяете вы сами, размещая на чертеже схемное обозначение «земли». В

Удаление смещения по оси амплитуды

Удаление смещения по оси амплитуды Может случиться так, что между звуковой картой и устройством ввода возникнут конфликты. Тогда излишек звукового потока добавляется к входящему сигналу, и конечная диаграмма сигналов отклоняется от нулевой оси. Это явление называется