Глава 2 Цифровая техника

Итак, рассмотрев какие виды микропроцессоров бывают и для решения каких видов задач они применяются, можно приступить к решению вопроса — как же они устроены? Как уже говорилось, микропроцессорная техника является частью цифровой техники. Поэтому, не зная основ цифровой техники, невозможно понять, как работает микропроцессор.

Начнем с самых элементарных вопросов: из каких элементов строятся цифровые схемы и как они устроены? Затем научимся реализовывать на основе этих простейших элементов цифровые устройства любой сложности. Следует отметить, что в данной книге вы не получите обзора всего разнообразия цифровых устройств. Будут рассмотрены только те цифровые устройства, которые используются непосредственно в микропроцессорной технике.

В данной главе будут рассмотрены только сумматоры и устройства коммутации цифровых сигналов. Однако, при необходимости, можно и разобраться в оставшихся за рамками данной книги разделах цифровой техники, применив рассмотренные методы построения цифровых устройств.

Обычно любые устройства предназначены для преобразования входных сигналов в выходные. Свойства аналоговых схем описываются рядом общепринятых параметров (например, коэффициентом усиления и динамическим диапазоном) и характеристик (амплитудно-частотные и фазо-частотные характеристики).

Иначе обстоит дело с параметрами цифровых микросхем. Для идеализированных цифровых устройств коэффициент усиления не нормируется — он реализуется достаточным для того, чтобы сигнал на выходе не затухал. И только! Логические уровни на входе и выходе цифровых микросхем одинаковы. Если логический элемент обладает запасом по коэффициенту усиления, то выходной сигнал просто ограничивается. Конкретное значение логических уровней зависит от напряжения питания цифровых микросхем и примененной схемотехники, но это не меняет принципов работы цифрового устройства.

Цифровые схемы наиболее полно описываются таблицей истинности.

Таблица истинности позволяет поставить выходные сигналы в соответствие входным сигналам. Обычно каждый из выходных сигналов цифрового устройства зависит от нескольких входных сигналов этого цифрового устройства. Поэтому в таблице истинности перечисляются все возможные комбинации входных сигналов и записывают соответствующий каждой комбинации входных сигналов выходной сигнал.

Достаточно часто одним и тем же комбинациям входных цифровых сигналов соответствуют несколько выходных сигналов. Тогда для всех выходных сигналов записывается одна таблица истинности.

Для простейших цифровых логических элементов таблица истинности состоит из одного выходного и одного или двух входных сигналов. Рассмотрим эти элементы.

Простейшие логические элементы

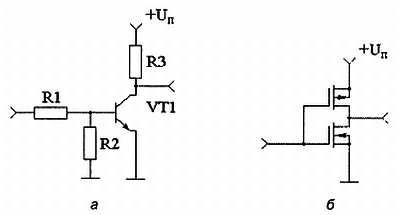

Любые цифровые устройства строятся на основе простейших логических элементов: «НЕ», «ИЛИ», «И». Самым простым логическим элементом является инвертор (элемент «НЕ»), который работает в соответствии с табл. 2.1. Он просто изменяет значение входного сигнала на прямо противоположное. В качестве инвертора можно использовать обычный транзисторный усилитель, построенный по схеме с общим эмиттером или общим истоком. Схемы, позволяющие реализовать функцию логического инвертирования, изображены на рис. 2.1. На рис. 2.1, а приведена схема инвертора на обычном биполярном транзисторе, а на рис. 2.1, б приведена схема инвертора, выполненного на комплементарных МОП-транзисторах.

Рис. 2.1. Схемы, реализующие функцию логического инвертирования

Условное графическое обозначение инвертора на схемах не зависит от схемотехники, использованной для его реализации, оно приведено на рис. 2.2. С этого момента инвертор будет изображаться исключительно в таком виде.

Рис. 2.2. Условное графическое обозначение инвертора

Следующий распространенный элемент цифровой техники реализует логическую операцию «И», однако чаще всего в качестве готовых микросхем существуют не отдельные схемы логического «И», а более сложные устройства, выполняющие одновременно две логические функции: «И» и «НЕ». Таблица истинности элемента, выполняющего логическую функцию «2И-НЕ», приведена в табл. 2.2.

Проще всего построить такой элемент на самых обыкновенных ключах, как это показано на рис. 2.3, а. В этой схеме ток будет протекать только в том случае, если оба ключа окажутся замкнутыми (будем считать, что такое их состояние достигается при управлении логической единицей). Это означает, что нулевой уровень на выходе схемы появится только при двух логических единицах на входе, т. е. приведенная схема реализует логическую функцию «2И-НЕ» (табл. 2.2). Точно таким же образом выполняется элемент «2И-НЕ» и в микросхемах, построенных на КМОП-транзисторах, только в качестве ключа используется транзистор. Схема логического элемента «2И-НЕ», выполненного на комплементарных МОП-транзисторах, приведена на рис. 2.3, б.

Рис. 2.3. Принципиальные схемы цифровых элементов, реализующих логическую функцию «2И-НЕ»

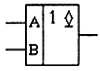

Условное графическое обозначение элемента, выполняющего логическую функцию «2И-НЕ», приведено на рис. 2.4, и с этого момента элементы, выполняющие данную функцию, будут изображаться именно в таком виде. Это обозначение не зависит от конкретной схемы построения цифрового элемента.

Рис. 2.4. Условное графическое обозначение цифрового элемента, выполняющего логическую функцию «И-НЕ»

Точно так же, как редко можно встретить отдельный элемент логического «И», практически не производятся отдельные элементы логического «ИЛИ». Чаще встречаются элементы «2ИЛИ-НЕ», таблица истинности которых приведена в табл. 2.3.

Как и в предыдущем случае, воспользуемся для реализации элемента «2ИЛИ-НЕ» ключами. На этот раз соединим ключи параллельно. Схема, реализующая таблицу истинности табл. 2.3, приведена на рис. 2.5, а. Схема логического элемента «2ИЛИ-НЕ», выполненного на КМОП-транзисторах, показана на рис. 2.5, б. Как видно из приведенных схем, уровень логического нуля появится на выходе любой из этих схем, как только любой из ключей будет замкнут, т. е. приведенные схемы реализуют таблицу истинности табл. 2.3.

Рис. 2.5. Принципиальные схемы элемента, реализующего логическую функцию «2ИЛИ-НЕ»

Так как один и тот же логический элемент может быть реализован различными способами, для его изображения на схемах используется специальное условное графическое обозначение, приведенное на рис. 2.6.

Рис. 2.6. Условное графическое обозначение элемента, выполняющего логическую функцию «2ИЛИ-НЕ»

Принципы реализации цифровых устройств по произвольной таблице истинности

Любое цифровое устройство полностью описывается таблицей истинности. При построении сложных устройств с произвольной таблицей истинности используется сочетание простейших элементов: «И» «ИЛИ» «НЕ». Если устройство имеет несколько выходов, то формирование сигнала для каждого из них анализируется отдельно и для каждого из них строится отдельная схема.

Для реализации устройства можно воспользоваться как элементами «И», так и элементами «ИЛИ». В настоящее время наиболее распространены микросхемы, совместимые с ТТЛ, а в ТТЛ проще всего получить элементы «И», выходы которых объединены по функции «ИЛИ», поэтому рассмотрим способ реализации произвольной таблицы истинности, основанный на комбинации логических элементов «И-ИЛИ».

Для реализации таблицы истинности при помощи логических элементов «И» достаточно рассмотреть только те ее строки, которые содержат логические единицы в выходном сигнале. Строки, содержащие в выходном сигнале логический ноль, в построении схемы не участвуют. Каждая строка, содержащая в выходном сигнале логическую единицу, реализуется элементом логического «И» с количеством входов, совпадающим с количеством входных сигналов в таблице истинности. Входные сигналы, описанные в таблице истинности логической единицей, подаются на вход этого элемента непосредственно, а входные сигналы, описанные в таблице истинности логическим нулем, подаются на вход этого же элемента «И» через инверторы. Объединение сигналов с выходов элементов «И», реализующих отдельные строки таблицы истинности, производится при помощи элемента логического «ИЛИ».

Количество входов элемента «ИЛИ» определяется количеством строк таблицы истинности, в которых в выходном сигнале присутствует логическая единица.

Для сокращения количества инверторов имеет смысл выделить их в отдельный блок, который сразу сформирует сигналы, инверсные по отношению к входным сигналам цифрового устройства. Теперь для реализации строки таблицы истинности достаточно соединить входы логического элемента «И» с соответствующими инвертированными и неинвертированными входными сигналами.

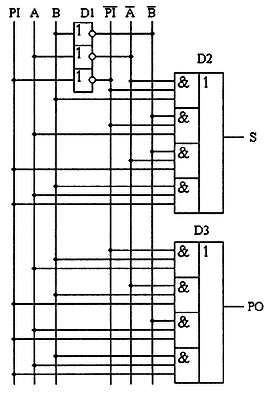

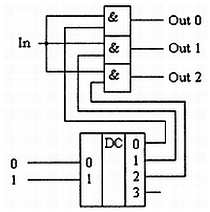

Рассмотрим конкретный пример. Пусть необходимо реализовать устройство с таблицей истинности, приведенной в табл. 2.4. Для построения схемы, реализующей сигнал Out1, достаточно рассмотреть строки, выделенные жирным шрифтом. Эти строки реализуются микросхемой D2 на рис. 2.7. Каждая строка реализуется своим многовходовым элементом «И», затем выходы этих элементов объединяются по «ИЛИ». Количество входов элемента «И» однозначно определяется числом входных сигналов в таблице истинности. Количество этих элементов, а значит и входов в логическом элементе «ИЛИ», определяется количеством строк с единичным сигналом на реализуемом выходе цифрового устройства.

Рис. 2.7. Принципиальная схема устройства, реализующего таблицу истинности, приведенную в табл. 2.4

Для построения схемы, реализующей сигнал Out2, достаточно рассмотреть строки, выделенные курсивом. Соответствующая логическая функция реализуется микросхемой D3. Принцип построения этой схемы такой же, как в примере, рассмотренном выше, и поэтому повторяться не будем.

Обычно при построении цифровых устройств после реализации таблицы истинности производится минимизация схемы, но для упрощения изложения материала в этой книге она выполняться не будет. Отказ от минимизации оправдан еще и тем, что неминимизированные схемы обычно обладают максимальным быстродействием.

Сумматоры

Важным элементом цифровых устройств, выполняющих арифметическую обработку цифровой информации, является сумматор. Построение двоичных сумматоров обычно начинается с сумматора по модулю 2. В табл. 2.5 приведена таблица истинности этого сумматора. Ее можно получить, исходя из правил суммирования в двоичной арифметике. Предполагается, что читатель знаком с основами двоичной арифметики. Более подробно операции над двоичными числами будут рассмотрены позднее.

В соответствии с принципами построения произвольной таблицы истинности, рассмотренными в предыдущей главе, получим схему сумматора по модулю 2. Эта схема приведена на рис. 2.8.

Рис. 2.8. Принципиальная схема устройства, реализующего таблицу истинности сумматора по модулю 2

Сумматор по модулю 2 (для двоичной арифметики его функцию реализует элемент исключающего «ИЛИ») изображается на схемах с использованием условного графического обозначения, показанного на рис. 2.9.

Рис. 2.9. Условное графическое обозначение элемента, выполняющего логическую функцию исключающего «ИЛИ»

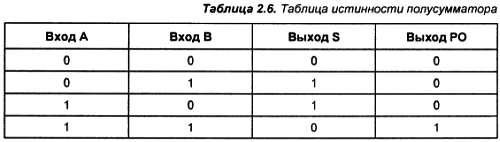

Сумматор по модулю 2 выполняет суммирование без учета переноса. В полном двоичном сумматоре его необходимо учитывать, поэтому требуются элементы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такого устройства, называемого полусумматором, приведена в табл. 2.6.

Обратите внимание, что сигналы в приведенной таблице истинности расположены в порядке, принятом для схем, т. е. в соответствии с тем, что сигнал распространяется слева направо. В результате перенос, который имеет двоичный вес, больший по сравнению с суммируемыми разрядами, записан правее. В математике принят другой порядок разрядов числа. Старший разряд на бумаге записывается самым левым, а младший разряд записывается самым правым. В результате может возникнуть путаница. Чтобы этого не произошло, приведу десятичный эквивалент каждой строки таблицы истинности полусумматора (табл. 2.6).

Первая строка получена из выражения 0 + 0 = 010 (002). Вторая строка получена из выражения 0 + 1 = 110 (012). Третья строка получена из выражения 1 + 0 = 110 (012). Четвертая строка получена из выражения 1 + 1 = 210(102).

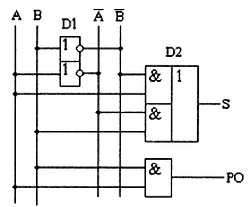

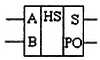

В соответствии с принципами построения произвольной таблицы истинности получим схему полусумматора. Она приведена на рис. 2.10. Условное графическое обозначение полусумматора показано на рис. 2.11.

Рис. 2.10. Принципиальная схема цифрового устройства, реализующего таблицу истинности полусумматора

Полусумматор формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому он и называется полусумматором.

Рис. 2.11. Условное графическое обозначение полусумматора

Таблицу истинности полного двоичного одноразрядного сумматора (табл. 2.7) можно получить из правил суммирования двоичных чисел.

В обозначении входов и выходов полного сумматора использовано следующее правило: в качестве входов использованы одноразрядные двоичные числа А и В; сумма — это одноразрядное двоичное число S; перенос обозначен буквой Р; для обозначения входа переноса используется сочетание букв PI (I — сокращение от английского слова input, вход); для обозначения выхода переноса используется сочетание букв РО (О — сокращение от английского слова output, выход).

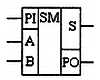

В соответствии с правилами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора. Она приведена на рис. 2.12.

Рис. 2.12. Принципиальная схема цифрового устройства, реализующая функцию полного двоичного одноразрядного сумматора

Ее можно минимизировать, но, как уже оговаривалось, минимизация в данной книге рассматриваться не будет. Условное графическое обозначение полного двоичного одноразрядного сумматора показано на рис. 2.13.

Рис. 2.13. Условное графическое обозначение полного двоичного одноразрядного сумматора

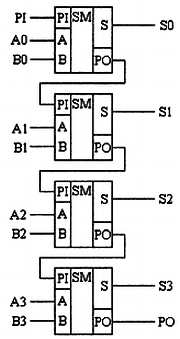

Для того чтобы получить многоразрядный сумматор, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Схема реализации четырехразрядного сумматора на основе четырех одноразрядных приведена на рис. 2.14.

Рис. 2.14. Принципиальная схема многоразрядного двоичного сумматора

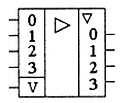

Одноразрядные сумматоры практически никогда не использовались, т. к. почти сразу же были выпущены микросхемы многоразрядных сумматоров. Полный двоичный четырехразрядный сумматор изображается на схемах с использованием условного графического обозначения, показанного на рис. 2.15.

Рис. 2.15. Условное графическое обозначение полного двоичного многоразрядного сумматора

Естественно, приведенная на рис. 2.14 схема не минимизирована, она служит лишь для пояснения принципа действия многоразрядного двоичного сумматора. В применяемых на практике схемах никогда не допускают последовательного распространения переноса через все разряды многоразрядного сумматора. Для увеличения скорости работы двоичного сумматора используется отдельная схема формирования переносов для каждого двоичного разряда. Таблицу истинности для такой схемы легко получить из алгоритма суммирования двоичных чисел, а затем применить хорошо известные нам принципы построения цифрового устройства по произвольной таблице истинности.

На этом пока закончим обсуждение принципов работы сумматора, более сложные операции будут рассмотрены позднее, а пока для дальнейшего понимания принципов работы микропроцессора необходимо разобраться, как осуществляется переключение двоичных чисел на входах и выходе сумматора. Эту операцию позволяют осуществить мультиплексоры и мультиплексоры, основной составной частью которых является дешифратор. Именно это цифровое устройство мы рассмотрим в следующем разделе.

Дешифраторы

Дешифраторы позволяют преобразовывать n-разрядный двоичный код в унитарный код с числом разрядов не более 2". Преобразование производится по таблицам истинности, поэтому построение принципиальных схем дешифраторов не представляет трудностей. Для этого можно воспользоваться рассмотренными ранее правилами построения цифрового устройства по произвольной таблице истинности.

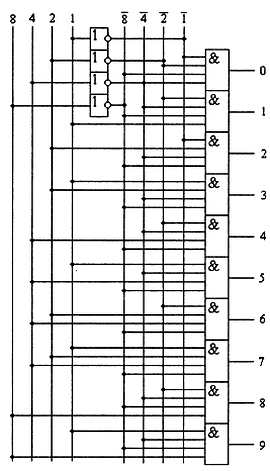

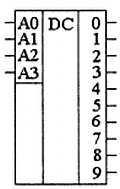

Рассмотрим пример построения дешифратора, который преобразует входной двоичный 4-разрядный двоичный код в унитарный 10-разрядный код. Данное устройство называют дешифратором 4x10. Его таблица истинности приведена в табл. 2.8.

В соответствии с принципами построения цифрового устройства по произвольной таблице истинности, описанными в предыдущей главе, получим схему дешифратора, реализующего таблицу истинности табл. 2.8.

Эта схема приведена на рис. 2.16.

Рис. 2.16. Принципиальная схема дешифратора 4x10

Точно так же можно получить схему для любого другого дешифратора. Дешифраторы выпускаются в виде отдельных микросхем или используются в составе других микросхем, таких как мультиплексоры или ПЗУ. Условное графическое обозначение дешифратора на схемах приведено на рис. 2.17. На этом рисунке показано обозначение дешифратора 4x10, принципиальная схема которого изображена на рис. 2.16.

Рис. 2.17. Условное графическое обозначение дешифратора 4x10

Мультиплексоры

Мультиплексорами называются устройства, которые позволяют подавать сигнал с одного из нескольких входов на один выход. В простейшем случае такую коммутацию можно осуществить при помощи ключей, изображенных на схеме рис. 2.18.

Рис. 2.18. Коммутатор, собранный на ключах

В цифровых устройствах нужно научиться управлять такими ключами цифровыми сигналами. Иными словами, мультиплексоры выполняют функцию ключа с электронным управлением цифровым сигналом.

Простейшим ключом с электронным управлением является логический элемент «И». Рассмотрим его таблицу истинности. Один из входов логического элемента «И» будем считать информационным, а другой вход — управляющим. Так как оба входа логического элемента «И» эквивалентны, то не важно, какой из них будет управляющим. Предположим, что вход X — управляющий, a Y — информационный. Для простоты рассуждений разделим таблицу истинности на две части в зависимости от уровня логического сигнала на управляющем входе X.

По таблице истинности отчетливо видно, что пока на управляющий вход X подан нулевой логический уровень, сигнал, поданный на вход Y на выход не проходит. При подаче на управляющий вход X логической единицы сигнал, поступающий на вход Y, появляется на выходе. То есть логический элемент «И» можно использовать в качестве электронного ключа. Остается только объединить выходы элементов «И». Это делается при помощи элемента «ИЛИ» точно так же, как и при построении схемы по произвольной таблице истинности. Такой вариант схемы коммутатора приведен на рис. 2.19.

Рис. 2.19. Принципиальная схема коммутатора, построенного на элементах «И»

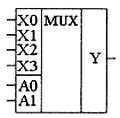

В схемах, приведенных на рис. 2.18 и 2.19, можно включать сразу несколько входов на один выход. Однако обычно это приводит к непредсказуемым последствиям. Кроме того, для управления таким коммутатором требуется много входов, поэтому в состав мультиплексора обычно включают двоичный дешифратор, как показано на рис. 2.20. Это позволяет управлять переключением информационных входов при помощи двоичных кодов, подаваемых на управляющие входы дешифратора. Количество информационных входов в таких схемах выбирают кратным степени числа два. Мультиплексор с двоичным управлением изображается на схемах как показано на рис. 2.21.

Рис. 2.20. Принципиальная схема мультиплексора, управляемого двоичным кодом

Рис. 2.21. Условное графическое обозначение мультиплексора

Демультиплексоры

Задача передачи сигнала с одного входа микросхемы на один из нескольких выходов называется демультиплексированием. Демультиплексор можно построить на основе точно таких же схем логического «И», как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных элементов. Однако для уменьшения входного тока демультиплексора на входе лучше поставить инвертор.

Схема демультиплексора приведена на рис. 2.22. Для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор.

Рис. 2.22. Принципиальная схема демультиплексора, управляемого двоичным кодом

На схемах демультиплексор обычно изображается точно так же, как и дешифратор, условное графическое обозначение которого приведено на рис. 2.17. Единственное отличие в изображении схемы — это наличие дополнительного информационного входа V. Условное графическое обозначение демультиплексора приведено на рис. 2.23.

Рис. 2.23. Условное графическое обозначение демультиплексора

Шинные формирователи

Мультиплексоры предназначены для выбора одного из нескольких сигналов в тех случаях, когда заранее известно их число. Часто это неизвестно. Более того, в ряде случаев количество микросхем, выходные сигналы которых выбираются мультиплексором, изменяется в процессе эксплуатации устройств. Наиболее яркий пример — это компьютеры, в которых в процессе эксплуатации изменяется объем оперативной памяти, количество портов ввода-вывода, количество дисководов. В таких случаях невозможно для объединения нескольких выходов ключей, реализованных на элементах «И», воспользоваться логическим элементом «ИЛИ».

Тем не менее, необходимо иметь возможность передавать информацию с нескольких выходов на один или несколько входов. Этого достигают, выделяя один или несколько проводников, по которым информация может передаваться в различных направлениях. Такая система проводников называется шиной.

Для объединения нескольких выходов на один вход в случае, когда заранее не известно, сколько микросхем нужно объединять, используется два способа:

— монтажное ИЛИ;

— шинные формирователи.

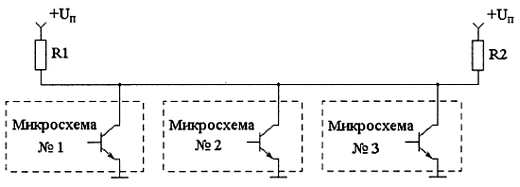

Исторически первым вариантом объединения выходов нескольких микросхем были схемы с открытым коллектором (монтажное «ИЛИ»). Схема монтажного «ИЛИ» приведена на рис. 2.24.

Рис. 2.24. Схема монтажного «ИЛИ»

Монтажное «ИЛИ» позволяет объединять до 10 микросхем на один провод. Естественно, для того, чтобы микросхемы не мешали друг другу, только одна из них должна выдавать информацию на линию шины. Остальные микросхемы в этот момент времени должны быть отключены от шины (т. е. выходной транзистор должен быть закрыт). Это обеспечивается внешней микросхемой управления, не показанной на данном рисунке. В качестве подобной микросхемы может служить обычный дешифратор.

На схемах логические элементы с открытым коллектором обозначаются, как это показано на рис. 2.25.

Рис. 2.25. Условное графическое обозначение микросхемы с открытым коллектором на выходе

Недостатком приведенной схемы объединения выходов нескольких микросхем на один провод является низкая скорость передачи информации, обусловленная затянутым передним фронтом. Это обусловлено тем, что ток заряда паразитной емкости шины проходит через сопротивления R1 и R2, которые много больше сопротивления открытого транзистора, обеспечивающего разряд этой емкости. Величину сопротивления нагрузки R1 и R2 невозможно снизить меньше некоторого предела, определяемого напряжением низкого уровня, который определяется в свою очередь допустимым током через выходной транзистор. В результате заряд происходит заметно медленнее, чем разряд. Временные диаграммы напряжений на входе и выходе микросхемы с открытым коллектором приведена на рис. 2.26.

Рис. 2.26. Временные диаграммы напряжений на входе и выходе микросхемы с открытым коллектором

Обратите внимание, что нагрузочные сопротивления включены на обоих концах проводника, образующего шину. Это позволяет уменьшить отражения сигнала от ненагруженных концов линии передачи сигнала, образованной данным проводником. Сопротивления резисторов R1 и R2 должны быть равны волновому сопротивлению этой линии передачи.

Естественным решением проблемы затягивания переднего фронта сигнала было бы включение транзистора в верхнее плечо схемы, но при этом возникает проблема сквозных токов, из-за которой невозможно соединять выходы цифровых микросхем непосредственно, и решением которой как раз является использование микросхем с открытым коллектором на выходе (монтажное «ИЛИ»). Причина возникновения сквозных токов поясняется на рис. 2.27. Показана ситуация, когда микросхема № 2 пытается сформировать на выходе уровень логической единицы, а микросхема № 1 — уровень логического нуля. Буквами «3» и «О» для выходных транзисторов обозначены закрытое и открытое состояния соответственно.

Рис. 2.27. Путь протекания сквозного тока Iскв при непосредственном соединении выходов цифровых микросхем

Эта проблема исчезает, если появляется возможность закрывать оба выходных транзистора, как в верхнем, так и в нижнем плече выходного каскада. Если оба транзистора закрыты, то такое состояние выхода микросхемы называется третьим состоянием или z-состоянием (высокоомным состоянием). Возможность переводить выход в третье состояние появляется в специализированных микросхемах. Принципиальная схема выходного каскада микросхемы с тремя состояниями на выходе приведена на рис. 2.28.

Рис. 2.28. Принципиальная схема выходного каскада микросхемы с тремя состояниями на выходе

В этой схеме вводится дополнительный управляющий вход, который может запирать оба выходных транзистора. В приведенной схеме это осуществляется закорачиванием баз обоих транзисторов на общий провод при помощи многоколлекторного транзистора, на базу которого сигнал управления подается через резисторы R1 и R2.

На схемах логические элементы с тремя состояниями на выходе обозначаются, как это показано на рис. 2.29.

Рис. 2.29. Условное графическое обозначение микросхемы с тремя состояниями на выходе

Часто в микросхеме, содержащей несколько выходных каскадов с тремя состояниями, объединяют управляющие сигналы всех выходов в один провод. Такие микросхемы используются для подключения многоразрядных устройств к шине микропроцессора и поэтому называются шинными формирователями. Шинные формирователи изображаются на схемах так, как показано на рис. 2.30.

Рис. 2.30. Условное графическое обозначение шинного формирователя

Итак, подведем итоги

В данной главе были рассмотрены простейшие логические элементы, а также устройства суммирования двоичных сигналов и устройства, которые позволят подавать на входы сумматора двоичные коды от различных источников информации. Кроме того, рассмотрены устройства, позволяющие подавать результат суммирования к различным средствам запоминания двоичных кодов.

Как будет показано в дальнейшем, любые, даже самые современные мощные микропроцессоры, из арифметических операций ничего, кроме суммирования, делать не умеют! Все их поражающие воображение вычислительные возможности сводятся к способности с огромной скоростью суммировать двоичные числа.

А теперь научимся работать с двоичными числами: суммировать их, вычитать, работать со знаком и с дробными числами. Кроме того, пора бы научиться работать и с обычными текстами!

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК