Глава 3 Запоминающие устройства

В предыдущей главе были рассмотрены основные виды микросхем, используемых в цифровой технике. Однако мы собирались строить цифровые устройства на базе микропроцессорной техники. Пора обсудить, как устроены блоки, входящие в состав микропроцессоров.

Одной из важнейших задач при построении универсальных устройств обработки информации является запоминание различных видов данных. Для выполнения этой функции были разработаны несколько видов микросхем, отличающихся друг от друга. Отличие связано с требованиями, предъявляемыми к хранимым данным. Часть из них должна существовать длительное время, часто до тех пор, пока существует устройство.

Другая часть данных представляет интерес только в течение относительно короткого промежутка времени, в процессе работы устройства. В зависимости от этих требований различается и внутреннее устройство микросхем.

Достаточно часто при длительном хранении данных требуется только операция считывания. При этом их можно записать в процессе изготовления устройства. Поэтому такие микросхемы получили название постоянных запоминающих устройств. Так как в этих микросхемах производится только одна операция, то и внутреннее устройство у них проще. Именно по этой причине начнем изучение внутренней структуры запоминающих устройств с постоянных запоминающих устройств.

Постоянные запоминающие устройства

Очень часто в различных устройствах требуется хранение информации, которая не изменяется. Это программы в микроконтроллерах, начальные загрузчики и BIOS в компьютерах, таблицы коэффициентов цифровых фильтров в сигнальных процессорах. Практически всегда эта информация не требуется вся сразу, обычно требуется доступ к отдельным ее фрагментам.

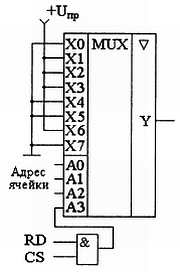

Простейшие устройства для запоминания постоянной информации можно построить на мультиплексорах. Схема такого постоянного запоминающего устройства приведена на рис. 3.1; это устройство содержит восемь одноразрядных ячеек памяти. Запоминание конкретного бита в одноразрядной ячейке производится присоединением соответствующего входа мультиплексора к источнику питания (высокий уровень — запись единицы) или к общему проводу (низкий уровень — запись нуля). Выбор конкретной ячейки памяти осуществляется при помощи адресных входов А0-А2. В приведенной на рис. 3.1 схеме — это входы управления мультиплексора.

Рис. 3.1. Схема постоянного запоминающего устройства, построенного на мультиплексоре

Обычно информация на выходе ПЗУ не требуется постоянно. Она должна быть предоставлена только по специальному запросу. Этот запрос формируется посредством сигнала чтения RD. Название этого сигнала расшифровывается как read (читать). Сигнал RD можно завести на внутренний дешифратор мультиплексора, как это показано на рис. 3.1. То есть содержимое ячейки памяти появится на выходе ПЗУ только при активном сигнале чтения RD. При всех других условиях выход микросхемы будет оставаться в высокоомном состоянии.

При построении устройств памяти обычно требуется иметь возможность расширения объема памяти. Это выполняется с помощью дополнительной микросхемы и дополнительной линии адресной шины. Кроме того, добавляется дешифратор адреса. Его нужно таким образом подключить к микросхемам памяти, чтобы он запрещал работу одной из микросхем памяти или разрешал работу другой в зависимости от адреса читаемой ячейки. Для подключения дополнительного дешифратора адреса служит еще один вход выбора кристалла CS (chip select — выбор кристалла). С точки зрения функционирования ПЗУ сигналы чтения RD и выбора кристалла CS не различаются, поэтому их можно объединить при помощи логического элемента «2И».

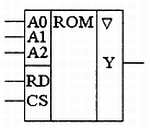

На схемах ПЗУ обозначается, как показано на рис. 3.2. На нем приведено условное графическое обозначение, соответствующее схеме рис. 3.1. Надпись «ROM» в среднем поле является сокращением от английских слов read-only memory (память, доступная только для чтения).

Рис. 3.2. Условное графическое обозначение постоянного запоминающего устройства

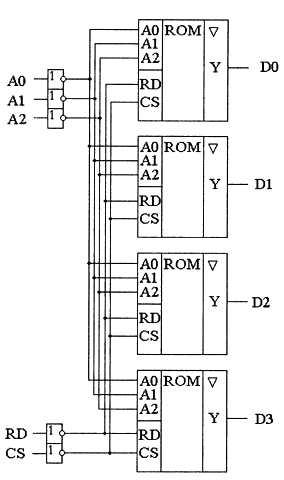

Для того чтобы увеличить разрядность ячейки памяти ПЗУ, одноразрядные микросхемы можно объединять. При этом параллельно соединяются одноименные адресные входы и входы сигналов управления RD и CS, a информационные выходы остаются независимыми. Схема объединения одноразрядных ПЗУ для реализации многоразрядного запоминающего устройства с восемью 4-разрядными ячейками приведена на рис. 3.3, а условное графическое обозначение 8-разрядного ПЗУ с 1024 ячейками памяти — на рис. 3.4.

Рис. 3.3. Схема многоразрядного ПЗУ

Как видно из приведенной схемы, адресные входы схемы объединяются параллельно. При этом возрастает общий входной ток микросхем памяти, протекающий по каждой линии адресной шины. Чтобы в результате не увеличивался входной ток запоминающего устройства, на адресных входах предусматривают усилители сигнала. В этом качестве можно использовать самые обыкновенные инверторы, как это показано на рис. 3.3. Точно с такой же целью поставлены инверторы и на управляющих входах чтения RD и выбора кристалла CS. При этом активными становятся низкие уровни этих сигналов.

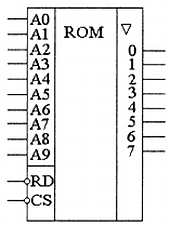

Масочные ПЗУ изображаются на схемах как показано на рис. 3.4. Активность низких уровней сигналов CS и RD обозначена кружками возле соответствующих управляющих входов.

Рис. 3.4. Условное графическое обозначение многоразрядного постоянного запоминающего устройства

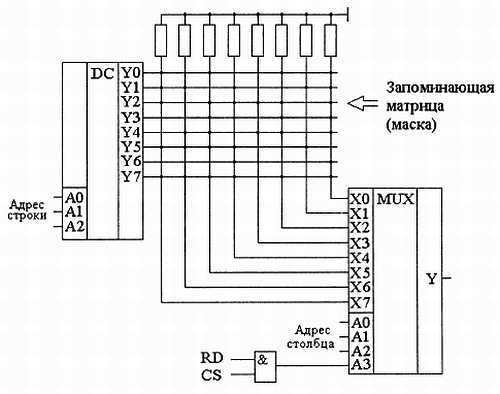

Запись информации в ПЗУ (микросхему, доступную только для чтения) производится при помощи последней операции изготовления микросхемы — металлизации. Она выполняется при помощи маски, поэтому такие микросхемы получили название масочных запоминающих устройств. Еще одно отличие реальных микросхем от упрощенной модели, приведенной выше, — это использование для дешифрации адреса кроме мультиплексора, еще и дешифратора. Такое решение позволяет превратить одномерную запоминающую структуру в двухмерную и тем самым существенно сократить объем схемы внутреннего дешифратора адреса. Реализация ПЗУ с двухмерной структурой запоминающих элементов показана на рис. 3.5.

Рис. 3.5. Схема масочного постоянного запоминающего устройства с двухмерной матрицей запоминающих элементов

Рассмотрим подробнее работу этого ПЗУ. В отличие от схемы, приведенной на рис. 3.1, в данном случае не используется непосредственное соединение входов мультиплексора с общим проводом. Вместо этого подключение производится через резистор. В результате, если с выхода дешифратора не будет подан единичный уровень, то на входе мультиплексора будет присутствовать уровень логического нуля. Запись логической единицы в ячейку ПЗУ производится соединением линий выхода дешифратора и входа мультиплексора в точке их пересечения. Если же в ячейку необходимо записать логический ноль, то соединение цепей не производится. Именно такая запоминающая структура получила название «матрица».

Приведенная на рис. 3.5 схема реализует одноразрядное ПЗУ с 64 одноразрядными ячейками памяти. Рассмотрим, какая информация хранится в этом ПЗУ. При выборе нулевой ячейки памяти на адресные входы дешифратора будут поданы три младших разряда адреса, т. е. код 000. В результате единичный уровень появится на выходе Y0. На адресные входы мультиплексора будут поданы старшие три разряда адреса. В нашем примере они тоже равны нулю. В результате мультиплексор передаст на выход сигнал со своего входа Х0. Так как на схеме эти цепи соединены между собой, то на выходе ПЗУ появится логическая единица.

Теперь рассмотрим считывание восьмой ячейки памяти. Здесь, как и в предыдущем случае, младшие три разряда адреса равны 0. Поэтому дешифратор выдаст единицу на линию Y0. Мультиплексор же получит код 001, поэтому на выход будет подключен вход XI. Эти цепи между собой не соединены, поэтому на выход будет выдан уровень логического нуля.

Для реализации многоразрядного ПЗУ необходимо использование нескольких матриц, подобных приведенной на рис. 3.5. Объединение матриц производится согласно схеме рис. 3.3.

Программирование масочного ПЗУ производится на заводе — изготовителе микросхем в процессе последнего этапа изготовления микросхемы — металлизации. Масочные ПЗУ широко применяются при крупносерийном производстве, т. к. являются самым дешевым видом ПЗУ. Однако использование подобных ПЗУ очень неудобно для мелко- и среднесерийного производства, не говоря уже о стадии разработки устройства, когда требуется многократная запись промежуточных вариантов программы. Для подобных вариантов применения были разработаны микросхемы, которые можно однократно программировать не на заводе — изготовителе микросхем, а в специальных устройствах — программаторах. В этих микросхемах ПЗУ постоянное соединение проводников в запоминающей матрице заменяется плавкими перемычками, изготовленными из поликристаллического кремния. Так как внутренняя схема такой микросхемы такая же, как у масочного ПЗУ, то для иллюстрации внутреннего устройства этой схемы можно воспользоваться рис. 3.5, предполагая при этом, что во всех точках пересечения вертикальных и горизонтальных проводников находятся плавкие поликремниевые перемычки.

При производстве микросхемы изготавливаются все перемычки, что эквивалентно записи во все ячейки памяти логических единиц. В процессе программирования на выводы питания и выходы микросхемы подается повышенное напряжение или низкий потенциал. При этом если на выход микросхемы подается повышенное напряжение питания (логическая единица), то через перемычку ток протекать не будет, и она останется неповрежденной. Если же на выход микросхемы в режиме программирования подать низкий уровень напряжения (присоединить к общему проводу), то через перемычку будет протекать ток, который испарит ее, и при последующем считывании информации из этой ячейки будет считываться логический ноль.

Микросхемы, работающие по такому принципу, называются (однократно) программируемыми ПЗУ (ППЗУ) и изображаются на схемах в виде условного графического обозначения, показанного на рис. 3.6. Надпись PROM в центральной части микросхемы является сокращением от английских слов programmable read-only memory (программируемая память, доступная только для чтения). В качестве примера таких ПЗУ можно назвать отечественные микросхемы 155РЕЗ, 556РТ4, 556РТ8.

Рис. 3.6. Условное графическое обозначение однократно программируемого постоянного запоминающего устройства

Однократно программируемые ПЗУ оказались очень удобными при мелко- и среднесерийном производстве, однако при разработке радиоэлектронных устройств часто приходится менять записываемую в ПЗУ программу. ППЗУ невозможно использовать повторно, поэтому при необходимости изменить содержимое памяти, записанное ППЗУ приходится выкидывать, что естественно повышает стоимость разработки аппаратуры. Для устранения этого недостатка был разработан еще один вид ПЗУ, содержимое которого могло бы стираться и программироваться многократно.

Примером такого устройства является ПЗУ с ультрафиолетовым или электрическим стиранием, которое строится на основе матрицы запоминающих элементов, внутреннее устройство одного из которых приведено на рис. 3.7.

Рис. 3.7. Запоминающий элемент ПЗУ с ультрафиолетовым и электрическим стиранием

Ячейка представляет собой МОП-транзистор, в котором затвор выполняется из поликристаллического кремния. Затем в процессе изготовления микросхемы этот затвор окисляется и в результате он оказывается окруженным оксидом кремния — диэлектриком с прекрасными изолирующими свойствами. Из-за того, что затвор со всех сторон окружен диэлектриком, он как бы плавает внутри диэлектрика, поэтому его называют плавающим затвором.

В описанной ячейке при полностью стертом ПЗУ заряда в плавающем затворе нет, и поэтому транзистор ток не проводит. При программировании микросхемы на программирующий электрод, находящийся над плавающим затвором, подается высокое напряжение и в последнем за счет туннельного эффекта индуцируются заряды. После снятия программирующего напряжения на плавающем затворе индуцированный заряд сохраняется и, следовательно, транзистор остается в проводящем состоянии. Заряд на плавающем затворе может храниться десятки лет.

Структурная схема постоянного запоминающего устройства не отличается от описанного ранее масочного ПЗУ. Единственное отличие — это использование описанной выше ячейки вместо плавкой поликремниевой перемычки. Такой вид ПЗУ в отечественной литературе получил название «репрограммируемые ПЗУ» (РПЗУ).

Стирание ранее записанной информации в репрограммируемых ПЗУ осуществляется ультрафиолетовым излучением. Для того чтобы оно могло беспрепятственно воздействовать на полупроводниковый кристалл, в корпус микросхемы РПЗУ встраивается окошко из кварцевого стекла. При облучении микросхемы изолирующие свойства оксида кремния теряются, накопленный заряд из плавающего затвора стекает в объем полупроводника, и транзистор запоминающей ячейки переходит в закрытое состояние. Время стирания микросхемы колеблется в пределах 10–30 минут.

Количество циклов записи-стирания микросхем РПЗУ составляет от 10 до 100 раз, после чего вследствие разрушающего действия ультрафиолетового излучения микросхема выходит из строя. В качестве примера таких микросхем можно назвать микросхемы 573-й серии российского производства, микросхемы серий 27сХХХ зарубежного производства.

В этих микросхемах чаще всего хранятся программы BIOS универсальных компьютеров. Репрограммируемые ПЗУ изображаются на схемах в виде условного графического обозначения, показанного на рис. 3.8.

Рис. 3.8. Условное графическое обозначение репрограммируемого постоянного запоминающего устройства

Надпись «EPROM» в центральной части микросхемы является сокращением от английских слов erasable programmable read-only memory (стираемая программируемая память, доступная только для чтения).

Из-за дороговизны корпуса с кварцевым окошком, а также вследствие такого недостатка, как сравнительно малое количество циклов записи/стирания, начали поиск способов стирания информации из РПЗУ электрическим потенциалом. На этом пути встретилось много трудностей, которые к настоящему времени практически решены. Сейчас достаточно широко распространены микросхемы с электрическим стиранием информации. В них используются такие же запоминающие ячейки, как и в РПЗУ, но они стираются электрическим потенциалом, поэтому количество циклов записи/стирания для этих микросхем достигает 1 млн раз.

Время стирания ячейки памяти в таких микросхемах уменьшается до 10 мс. В настоящее время наметилось два направления развития микросхем РПЗУ:

1. ЭСРПЗУ — электрически стираемые ПЗУ.

2. Флэш-ПЗУ.

Из-за сложности внутренней схемы управления запоминающими элементами электрически стираемые ПЗУ дороже и меньше по объему, но зато позволяют перезаписывать каждую ячейку памяти отдельно. В результате эти микросхемы обладают максимальным количеством циклов записи/стирания. Область применения электрически стираемых ПЗУ — хранение данных, которые не должны разрушаться при выключении питания.

К таким микросхемам относятся отечественные микросхемы 573РРЗ и зарубежные микросхемы серии 28сХХ. Электрически стираемые ПЗУ изображаются на схемах при помощи условного графического обозначения, показанного на рис. 3.9. Надпись «EEPROM» в среднем поле расшифровывается как electrically erasable programmable read-only memory — электрически стираемая программируемая память, доступная только для чтения.

Рис. 3.9. Условное графическое обозначение электрически стираемого постоянного запоминающего устройства

В последнее время наметилась тенденция уменьшения габаритов ЭСРПЗУ за счет сокращения количества внешних выводов микросхем. Для этого адрес и данные передаются в микросхему и из микросхемы в виде последовательного кода. При этом используются два вида последовательных интерфейсов: SPI и I2C (микросхемы серий 93сХХ и 24сХХ соответственно). Зарубежной серии 24сХХ соответствует отечественная серия микросхем 558РРх.

Микросхемы флэш-ПЗУ отличаются от ЭСРПЗУ тем, что производится стирание не каждой ячейки отдельно, а всей запоминающей матрицы, как это делалось в РПЗУ, или ее части (блока). Условное графическое обозначение FLASH-ПЗУ на схемах приведено на рис. 3.10.

Рис. 3.10. Условное графическое обозначение FLASH-памяти

Использование блочного стирания позволяет уменьшить сложность внутреннего устройства управления микросхем, поэтому FLASH-ПЗУ предоставляют максимальный объем матрицы запоминающих элементов. Кроме того, эти микросхемы обладают значительно меньшей стоимостью по сравнению с электрически стираемыми ПЗУ. В настоящее время FLASH-ПЗУ постепенно вытесняют все остальные виды постоянных запоминающих устройств за исключением электрически стираемых ПЗУ.

Рассмотренные виды памяти позволяют хранить информацию практически неограниченно долго. Тем не менее, они не обладают максимальным быстродействием, поэтому, кроме постоянных запоминающих устройств, используются более быстродействующие микросхемы, теряющие свое содержимое при выключении питания. Эти микросхемы обладают большим быстродействием по сравнению с ПЗУ и в них записывают результаты предварительных вычислений или информацию, нужную только в определенный момент времени. Например, набранный номер вызываемого абонента в сотовом аппарате или выбранный номер телевизионной программы в телевизоре.

Для хранения информации можно воспользоваться элементами, которые сохраняют напряжение на своем выходе до тех пор, пока подается питание. Элементы, которые могут запоминать двоичные логические уровни, получили название «триггеры». Рассмотрим подробнее, как устроены подобные устройства.

Триггеры

Простейшая схема, позволяющая запоминать двоичную информацию, строится на основе простейших логических элементов «ИЛИ» или «И», описанных в главе 1. Такая схема, построенная на элементах «И», приведена на рис. 3.11. Выход триггера Q можно установить в единичное состояние при подаче на его вход S (Set) логического нуля. Сбросить выход триггера Q в нулевое состояние можно, подав на его вход R (Reset) логический ноль. Это состояние сохраняется до подачи очередного сигнала R или S либо до выключения напряжения питания схемы.

Так как описанный триггер можно только устанавливать в единичное значение или сбрасывать в нулевое значение, он получил название RS-триггер.

Рис. 3.11. Схема простейшего триггера на элементах «И»

Входы R и S инверсные (активный уровень '0')

Такой триггер можно построить и на логических элементах «ИЛИ». Такая схема приведена на рис. 3.12. Единственное отличие от схемы рис. 3.11 будет заключаться в том, что сброс и установка триггера осуществляются единичными логическими уровнями.

Рис. 3.12. Схема простейшего триггера на элементах «ИЛИ»

Входы R и S прямые (активный уровень '1')

Так как триггер при построении его на различных логических элементах работает одинаково, то его изображают на схемах тоже одинаково.

Условное графическое обозначение RS-триггера приведено на рис. 3.13.

Рис. 3.13. Условное графическое обозначение простейшего триггера

Триггер позволяет запоминать логический сигнал, но при изменении сигнала на входе устройства может возникать переходный процесс (в цифровых схемах это явление называют гонками или состязаниями), в ходе которого сигнал на входе триггера может принимать случайные значения. Это может привести к ошибкам, для предотвращения которых запоминание входного сигнала должно происходить после окончания всех переходных процессов. То есть цифровые схемы требуют синхронизации. Все переходные процессы в цифровой схеме должны закончиться до поступления синхросигнала, иначе цифровое устройство будет работать с ошибками.

В синхронных цифровых схемах используются синхронные триггеры. Для построения такого триггера можно воспользоваться логическим элементом «И», ведь он может работать как электронный ключ (см. построение мультиплексора на рис. 2.18). Схема синхронного RS-триггера приведена на рис. 3.14, а его условное графическое обозначение — на рис. 3.15.

Рис. 3.14. Схема синхронного триггера на схемах «И»

Рис. 3.15. Условное графическое обозначение синхронного триггера

В дальнейшем именно это обозначение и будет использоваться на схемах более сложных запоминающих устройств.

В приведенных схемах триггеров для записи логического нуля и логической единицы требуется подавать сигналы на разные входы, что не всегда удобно, поэтому для запоминания дискретной информации применяются D-триггеры, имеющие один информационный вход. В D-триггере достаточно подать на вход D сигнал, который необходимо запомнить, и синхроимпульс — на вход синхронизации С. Схема такого триггера приведена на рис. 3.16, а условное графическое обозначение — на рис. 3.17.

Рис. 3.16. Схема D-триггера со статическим управлением (защелки)

Рис. 3.17. Условное графическое обозначение D-триггера со статическим управлением (защелки)

Во всех приведенных схемах триггеров запоминание сигнала происходит по уровню синхросигнала, поэтому они называются D-триггерами со статическим управлением, или триггерами-защелками. Легче всего объяснить появление этого названия по временным диаграммам, приведенным на рис. 3.18.

Рис. 3.18. Временные диаграммы D-триггера со статическим управлением (защелки)

Как видно из рисунка, триггер-защелка хранит данные только при нулевом уровне на входе синхронизации С. Если же на этот вход подать активный высокий уровень, то напряжение на выходе триггера будет повторять входной сигнал. Входное напряжение запоминается только в момент изменения уровня сигнала синхронизации С с высокого на низкий. Входные данные как бы «защелкиваются» в этот момент, отсюда и название — триггер-защелка.

В этой схеме переходный процесс входного информационного сигнала (D) может беспрепятственно проходить на выход триггера. Поэтому там, где важно избежать этого, необходимо сокращать длительность импульса синхронизации до минимума. Только в этом случае переходный процесс практически не сможет появиться на выходе триггера.

Чтобы преодолеть такое ограничение на длительность синхронизирующего импульса, были разработаны триггеры, работающие по фронту синхросигнала. Схема такого триггера приведена на рис. 3.19, а его условное графическое обозначение — на рис. 3.20.

Рис. 3.19. Схема D-триггера с управлением по фронту

Рис. 3.20. Условное графическое обозначение D-триггера с управлением по фронту

Как видно из схемы D-триггера с управлением по фронту, приведенной на рис. 3.19, на ее выходе не могут появиться переходные процессы, т. к. если их пропускает первый триггер, то не пропустит второй, который в это время находится в режиме хранения. И наоборот, если второй триггер пропускает сигнал со своего входа на выход, то первый триггер находится в режиме хранения и, значит, сигнал на входе второго триггера не может измениться.

Из рис. 3.19 видно, что схема триггера с управлением по фронту сложнее, чем у триггера-защелки, а это означает, что D-триггер с управлением по фронту будет дороже, а его быстродействие — ниже, чем у триггера-защелки.

Регистры

Триггеры позволяют запоминать одноразрядное двоичное слово. Однако в ряде случаев требуется запоминать двоичные слова большей разрядности. Это позволяют сделать регистры.

Регистром называется последовательное или параллельное соединение любых устройств, будь то клавиши музыкального инструмента, набор букв печатающей машинки или триггеры в цифровой технике. Регистры обычно строятся на основе D-триггеров. При этом для построения регистров могут использоваться как D-триггеры с управлением по фронту, так и триггеры-защелки. При использовании для этого защелок регистр называется регистром-защелкой. Параллельный регистр служит для запоминания многоразрядного двоичного слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырехразрядного параллельного регистра, построенного на D-триггерах, приведена на рис. 3.21, а его условное графическое обозначение — на рис. 3.22.

Рис. 3.21. Схема 4-разрядного параллельного регистра

Рис. 3.22. Условное графическое обозначение 4-разрядного параллельного регистра

При записи информации в параллельный регистр все биты (двоичные разряды) записываются одновременно, поэтому входы синхронизации всех триггеров можно соединить параллельно.

Кроме параллельных, в цифровой технике используются последовательные регистры. Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Схема регистра, осуществляющего преобразование последовательного кода в параллельный, приведена на рис. 3.23, а его условное графическое обозначение — на рис. 3.24.

Рис. 3.23. Схема последовательного регистра

Рис. 3.24. Условное графическое обозначение последовательного регистра

В схеме, приведенной на рис. 3.23, информация, поступившая на вход первого триггера сдвигового регистра D0, будет переписываться в следующий триггер при поступлении очередного синхронизирующего импульса. Таким образом, после четырех тактовых импульсов на выходах сдвигового регистра окажется записанной информация, присутствовавшая на входе регистра в моменты поступления этих тактовых импульсов.

Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы, что позволяет преобразовывать двоичный код из параллельной формы в последовательную. Это свойство универсального последовательно-параллельного регистра используется, например, для реализации последовательного порта в микропроцессорной системе. Схема универсального последовательно-параллельного регистра приведена на рис. 3.25, а его условное графическое обозначение — на рис. 3.26.

Рис. 3.25. Схема универсального последовательно-параллельного регистра

Рис. 3.26. Условное графическое обозначение универсального последовательно-параллельного регистра

Переключение регистра из параллельного режима в последовательный и наоборот осуществляется при помощи мультиплексора, построенного на элементах 2И-2ИЛИ (рис. 3.25). В зависимости от управляющего сигнала V он подключает к входу каждого D-триггера либо выход предыдущего триггера, либо параллельный вход универсального регистра. При подаче на вход управления V логической единицы регистр будет работать как параллельный, а при подаче логического нуля — как последовательный.

Если читателю покажется непонятной работа коммутатора, собранного на элементах 2И-2ИЛИ, то имеет смысл заново перечитать описание работы мультиплексора в главе 2.

Статические оперативные запоминающие устройства (ОЗУ)

В радиоаппаратуре часто требуется хранение временной информации, значение которой не важно при включении устройства. Такую память можно было бы построить на микросхемах EEPROM- или FLASH-памяти, но, к сожалению, эти микросхемы дороги, характеризуются сравнительно малым количеством циклов перезаписи, а также чрезвычайно низким быстродействием при считывании и особенно при записи информации. Для хранения временной информации можно воспользоваться параллельными регистрами.

Устройства памяти, в которых в качестве запоминающих ячеек используются параллельные регистры, называются статическими ОЗУ, т. к. информация в них сохраняется все время, пока к микросхеме подключено питание. Кроме микросхем статических ОЗУ, существуют микросхемы динамических ОЗУ, где в качестве запоминающих ячеек используются конденсаторы. В отличие от микросхем статического ОЗУ, в микросхемах динамического ОЗУ постоянно требуется регенерировать их содержимое, иначе из-за разряда конденсаторов информация будет испорчена. Эти микросхемы будут рассмотрены позднее.

Так как запоминаемые слова не нужны одновременно, то в ОЗУ можно воспользоваться механизмом адресации, который уже рассматривался ранее при объяснении принципов работы ПЗУ.

В микросхемах статических ОЗУ присутствуют две операции: запись и чтение. Для их выполнения можно использовать различные шины данных (как это делается в сигнальных процессорах), но чаще используется одна и та же шина. Это позволяет экономить выводы микросхем, подключаемых к этой шине, и легко осуществлять коммутацию сигналов между различными устройствами.

Схема статического ОЗУ приведена на рис. 3.27. Вход и выход микросхемы в этой схеме объединены при помощи шинного формирователя. Естественно, что схемы реальных ОЗУ будут иными, чем приведенная на этом рисунке. Тем не менее, она позволяет понять, как работает реальное ОЗУ статического типа. Условное графическое обозначение ОЗУ на схемах приведено на рис. 3.28.

Рис. 3.27. Структурная схема ОЗУ

Рис. 3.28. Условное графическое обозначение ОЗУ

На схеме рис. 3.27 для обозначения того, что используется инвертированный сигнал или сигнал с активным низким уровнем, над именем цепи проставляется черта. К сожалению, в обычном тексте затруднительно использовать такую же черту. Поэтому для обозначения таких сигналов в книге используется два способа: символ подчеркивания перед именем цепи (_WR) или символ # после имени (WR#).

Сигнал записи WR# позволяет записать логические уровни, присутствующие на информационных входах, во внутреннюю ячейку ОЗУ. Сигнал чтения RD# позволяет выдать содержимое внутренней ячейки памяти на информационные выходы микросхемы. В приведенной на рис. 3.27 схеме невозможно одновременно производить операцию записи и чтения, но это в большинстве случаев и не нужно. Схема на рис. 3.27 ориентирована на применение микропроцессорной системы с одной шиной, по которой в разные моменты времени будет осуществляться или запись, или чтение информации.

Конкретная ячейка микросхемы, в которую будет записываться информация, выбирается при помощи двоичного кода — адреса ячейки. Объем памяти микросхемы зависит от количества ячеек, содержащихся в ней.

Количество адресных выводов микросхемы ОЗУ однозначно определяется количеством находящихся в ней ячеек памяти. Исходя из этого, количество ячеек памяти М в микросхеме можно определить по количеству адресных выводов N. Для этого необходимо возвести число 2 в степень, равную количеству адресных выводов микросхемы:

М = 2N

Вывод выбора кристалла CS позволяет объединять несколько микросхем для увеличения объема памяти ОЗУ. Пример объединения четырех микросхем ОЗУ с помощью дешифратора приведен на рис. 3.29. При этом общий объем памяти увеличивается в четыре раза.

Рис. 3.29. Схема ОЗУ, построенного на нескольких микросхемах памяти

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их емкость (количество запоминающих элементов) относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных систем из-за простоты схемы запоминающих устройств на их основе и возможности работать при сколь угодно больших длительностях управляющих сигналов, вплоть до статического режима. Это позволяет свободно выбирать тактовую частоту и упрощает процедуру отладки микропроцессорной системы. Кроме того, статические ОЗУ применяются для построения кэш-памяти в универсальных компьютерах, т. к. они обладают более высоким быстродействием по сравнению с динамическими ОЗУ.

Временные диаграммы чтения данных из статического ОЗУ, такие же, как аналогичные диаграммы для рассмотренного ранее ПЗУ. Временные диаграммы записи в статическое ОЗУ и чтения из него приведены на рис. 3.30.

Рис. 3.30. Временная диаграмма обращения к ОЗУ, принятая для схем, совместимых с микропроцессорами фирмы Intel

На рис. 3.30 стрелочками показана последовательность, в которой должны формироваться управляющие сигналы. На этом рисунке RD — это сигнал чтения; WR — сигнал записи; А — сигналы шины адреса (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода сигнала как в единичное, так и в нулевое состояние); DI — входная информация, предназначенная для записи в ячейку ОЗУ, расположенную по адресу A1; DO — выходная информация, считанная из ячейки ОЗУ, расположенной по адресу А2.

Временная диаграмма, приведенная на рис. 3.30, не единственная, применяемая для построения микропроцессорных систем. Она была предложена фирмой Intel и получила широкое распространение. Для обращения к ОЗУ применяется и временная Диаграмма, предложенная фирмой Motorola. Эта временная диаграмма предполагает наличие постоянно присутствующего синхросигнала и сигнала, который определяет операцию, которую необходимо выполнить (запись или чтение).

Временная диаграмма микросхемы, работающей по описанному выше принципу, приведена на рис. 3.31. На этом рисунке стрелочками показана последовательность, в которой должны формироваться управляющие сигналы, при этом R/W — сигнал выбора операции записи или чтения; DS — сигнал стробирования данных; А — сигналы адресной шины (так как отдельные биты в шине адреса могут принимать разные значения, то показаны пути перехода сигнала как в единичное, так и в нулевое состояние); DI — входная информация, предназначенная для записи в ячейку ОЗУ, расположенную по адресу A1; DO — выходная информация, считанная из ячейки ОЗУ, расположенной по адресу А2.

Рис. 3.31. Временная диаграмма обращения к ОЗУ, принятая для схем, совместимых с микропроцессорами фирмы Motorola

Динамические оперативные запоминающие устройства (ОЗУ)

Статические ОЗУ позволяют обеспечивать хранение записанной информации до тех пор, пока на микросхему подается питание. Однако запоминающая ячейка статического ОЗУ занимает относительно большую площадь, поэтому для ОЗУ большого объема применяют более простую и потому компактную запоминающую ячейку — конденсатор. Естественно, что заряд на конденсаторе с течением времени уменьшается, поэтому его необходимо подзаряжать с периодом приблизительно 10 мс, называемым периодом регенерации. Подзарядка емкости производится при считывании ячейки памяти, поэтому для регенерации информации достаточно просто считать регенерируемую ячейку памяти.

Схема запоминающего элемента динамического ОЗУ и его конструкция приведены на рис. 3.32.

Рис. 3.32. Схема запоминающего элемента динамического ОЗУ и его конструкция

При считывании заряда емкости необходимо учитывать, что линия считывания имеет большую электрическую емкость, чем запоминающая ячейка. Графики, показывающие, как изменяется напряжение на линии считывания при выполнении операции чтения информации из запоминающей ячейки без использования схемы регенерации, приведены на рис. 3.33.

Рис. 3.33. Графики изменения напряжения на линии считывания при считывании информации с запоминающей ячейки

Первоначально на линии записи/считывания присутствует половина напряжения питания микросхемы. При подключении к линии записи/считывания запоминающей ячейки заряд, хранящийся в запоминающей ячейке, изменяет напряжение на линии на небольшую величину ΔU. Теперь это напряжение необходимо восстановить до первоначального логического уровня. Если приращение напряжения ΔU было положительным, то напряжение необходимо довести до напряжения питания микросхемы. Если приращение ΔU было отрицательным, то напряжение необходимо довести до потенциала общего провода.

Для регенерации первоначального заряда, хранившегося в запоминающей ячейке, в схеме применяется RS-триггер, включенный между двумя линиями записи/считывания. Схема такого регенерирующего устройства приведена на рис. 3.34.

Рис. 3.34. Схема регенерирующего каскада

Эта схема за счет положительной обратной связи восстанавливает первоначальное значение напряжения, хранившегося в запоминающей ячейке. При этом на соседней линии считывания формируется противоположный сигнал, но т. к. она в данный момент никуда не подключена, то это неважно. То есть при считывании ячейки производится регенерация хранящегося в ней заряда. Для уменьшения времени регенерации микросхема устроена так, что при считывании одной ячейки памяти в строке запоминающей матрицы регенерируется вся строка.

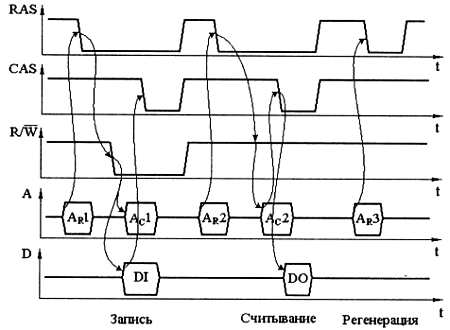

Особенностью использования динамических ОЗУ является мультиплексирование шины адреса. Адрес строки и адрес столбца передаются поочередно. Адрес строки синхронизируется стробирующим сигналом RAS# (Row Address Strobe), а адрес столбца — сигналом CAS# (Column Address Strobe). Мультиплексирование адресов позволяет уменьшить количество выводов микросхем ОЗУ, что очень важно для микросхем с большим объемом внутренней памяти, т. е. с большой разрядностью адресной шины. Условное графическое обозначение микросхемы динамического ОЗУ на схемах приведено на рис. 3.35, а временная диаграмма обращения к такой микросхеме — на рис. 3.36.

Рис. 3.35. Условное графическое обозначение динамического ОЗУ

Рис. 3.36. Временная диаграмма обращения к динамическому ОЗУ

Именно так долгое время велась работа с динамическими ОЗУ. Затем было замечено, что обычно обращение ведется к данным, лежащим в соседних ячейках памяти, поэтому не обязательно при считывании или записи каждый раз передавать адрес строки. Данные стали записывать или считывать блоками и адрес строки передавать только в начале блока. При этом можно сократить общее время обращения к динамическому ОЗУ и тем самым увеличить быстродействие компьютера.

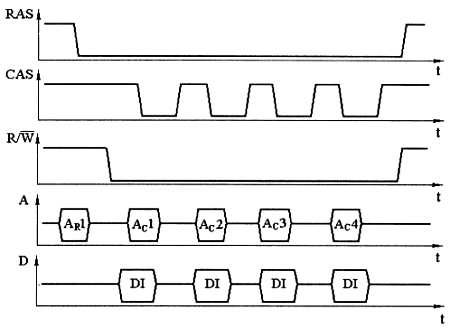

Такое обращение к динамическому ОЗУ называется быстрым страничным режимом доступа (FPM, Fast Page Mode). Длина считываемого блока данных обычно равна четырем словам. Время доступа к памяти принято оценивать в тактах системной шины процессора. В обычном режиме доступа к памяти оно одинаково для всех слов. Поэтому цикл обращения к динамической памяти можно записать как 5-5-5-5. При режиме быстрого страничного доступа цикл обращения к динамической памяти можно записать как 5-3-3-3, т. е. время обращения к первой ячейке не изменяется по сравнению с предыдущим случаем, а считывание последующих ячеек сокращается до трех тактов. При этом среднее время доступа к памяти сокращается почти в полтора раза. Временная диаграмма режима FPM приведена на рис. 3.37.

Рис. 3.37. Временная диаграмма записи в динамическое ОЗУ в режиме FPM

Еще одним способом увеличения быстродействия ОЗУ является применение микросхем EDO (Extended Data Out — ОЗУ с расширенным выходом данных). В EDO ОЗУ усилители-регенераторы не сбрасываются по окончанию строба CAS#, поэтому времени для считывания данных в таком режиме больше. Теперь для того чтобы сохранить время считывания на прежнем уровне, можно увеличить тактовую частоту системной шины и тем самым увеличить быстродействие компьютера. Для EDO ОЗУ цикл обращения к динамической памяти можно записать как 5-2-2-2.

Следующим шагом в развитии схем динамического ОЗУ было применение в составе ОЗУ счетчика столбцов. То есть при переходе адреса ячейки к следующему столбцу запоминающей матрицы адрес столбца инкрементируется (увеличивается) автоматически. Такое ОЗУ получило название BEDO (ОЗУ с пакетным доступом). В этом типе ОЗУ удалось достигнуть режима обращения к динамической памяти 5-1-1-1.

В синхронном динамическом ОЗУ (SDRAM) увеличение быстродействия получается за счет применения конвейерной обработки сигнала. Как известно, при использовании конвейера можно разделить операцию считывания или записи на отдельные подоперации, такие как выборка строк, выборка столбцов, считывание ячеек памяти, и производить эти операции одновременно. При этом пока на выход передается считанная ранее информация, производится дешифрация столбца для текущей ячейки памяти и производится дешифрация строки для следующей ячейки памяти. Этот процесс иллюстрируется рис. 3.38, а.

Из приведенного рисунка видно, что, несмотря на увеличение времени доступа к ОЗУ при считывании одной ячейки памяти, при считывании нескольких соседних ячеек памяти общее быстродействие микросхем синхронного динамического ОЗУ возрастает. Для сравнения на рис. 3.38, б приведена структурная схема обычного динамического ОЗУ.

Рис. 3.38. Структурная схема конвейерной обработки данных

Время задержки распространения сигнала tз в этой схеме равно периоду тактового сигнала в шине обращения к ОЗУ и определяется по формуле:

tз = tCT + tDC+ tЗМ,

где tCT — это время срабатывания счетчика адреса динамического ОЗУ; tDC — это время распространения сигнала дешифратора адреса; tЗМ — это время появления сигнала на выходе запоминающей матрицы.

Время задержки распространения сигнала в схеме синхронного динамического ОЗУ можно определить по формуле:

tз = tCT + tDC + tRG + tЗМ + tRG,

где tRG — это записи в параллельный регистр.

Таким образом, время доступа к синхронному динамическому ОЗУ больше, чем к обычному динамическому ОЗУ. Однако период тактового сигнала можно значительно уменьшить, т. к. он будет определяться максимальным из времен:

Поэтому, несмотря на то, что при обращении к одиночной ячейке памяти время доступа к SDRAM возрастает, при пакетном считывании последовательно расположенных байт общее время считывания оказывается значительно меньшим, т. к. все последующие данные на выходе ОЗУ будут появляться с периодом tобр. Выигрыш при пакетной работе SDRAM может быть достаточно большим, т. к. при обращении к этому типу памяти допустимо устанавливать размер пакета данных равным 256 слов.

На этом закончим рассмотрение различных видов памяти микропроцессорных устройств. Полученных знаний вполне достаточно для продолжения изложения материала. Если же кому-либо захочется более подробно ознакомиться с устройствами запоминания информации, можно обратиться к специализированной литературе [1, 3, 5–7].

Итак, подведем итоги

В данной главе были рассмотрены различные устройства хранения данных. Используя сумматоры, рассмотренные в предыдущей главе и запоминающие устройства, рассмотренные в этой главе, уже можно построить устройство обработки данных, входящее в состав любого микропроцессора.

А теперь научимся работать с двоичными числами: суммировать их, вычитать, работать со знаком и с дробными числами. Кроме того, пора бы научиться работать и с обычными текстами!

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОК