Bobcat и Bulldozer: новые микроархитектуры AMD Олег Нечай

Bobcat и Bulldozer: новые микроархитектуры AMD

Олег Нечай

Опубликовано 26 августа 2010 года

24 августа 2010 года компания Advanced Micro Deviced (AMD) обнародовала информацию о микроархитектурах нового поколения Bobcat и Bulldozer, которые найдут применение в серийных процессорах уже в будущем году.

Микроархитектура AMD Bobcat

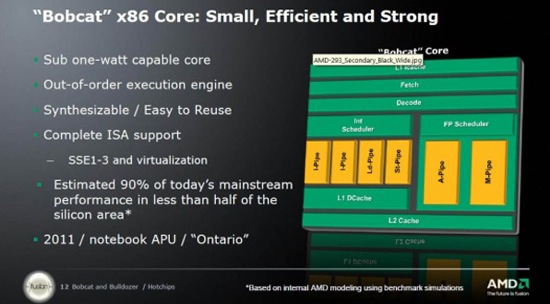

Микроархитектура AMD Bobcat разработана специально для энергоэффективных процессоров, рассчитанных на установку в нетбуках и неттопах. Главное достоинство этих микросхем – сверхнизкое энергопотребление, не превышающее одного ватта. При этом, в отличие от Intel Atom, построенных на классическом принципе последовательного исполнения инструкций (подробнее см. здесь), в Bobcat используется механизм внеочередного исполнения команд, типичный для «взрослых» мобильных и десктопных процессоров.

Первые чипы на основе микроархитектуры Bobcat будут выпущены уже в четвёртом квартале 2010 года. Эти двухъядерные процессоры со встроенным контроллером оперативной памяти и графическим ядром с поддержкой программного интерфейса DirectX 11 получат кодовое название Ontario. Микросхемы будут производиться по 32-нанометровой технологии. Крупнейшие производители ноутбуков, среди которых компании Acer, ASUS и Hewlett-Packard, уже объявили о намерении представить первые компьютеры на базе Ontario в первом квартале 2011 года.

Микроархитектура AMD Bulldozer

Процессорная микроархитектура AMD Bulldozer не имеет практически ничего общего с архитектурой AMD64, лежащей в основе современных чипов этой компании, так что о ней мы поговорим подробнее.

Что представляет собой эта архитектура и в чём её отличия от современной?

Как и следовало ожидать, в AMD Bulldozer используются некоторые решения, апробированные в предыдущих архитектурах. Прежде всего, речь идёт о встроенном в чип контроллере оперативной памяти — решении, фактически ставшем промышленным стандартом, а также скоростной шине HyperTransport для подключения процессора к системной логике.

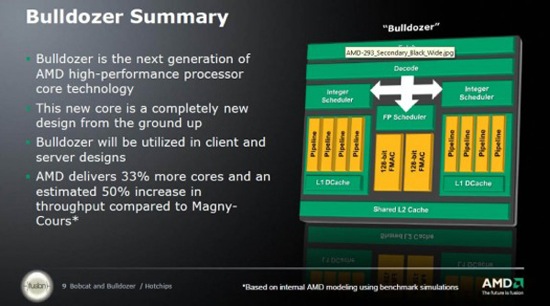

В отличие от чипов AMD64, «настоящих многоядерных» процессоров, что постоянно подчёркивали в AMD, в основу новой микроархитектуры положен принципиально иной подход. Процессоры следующего поколения будут состоять из одного или нескольких двухъядерных модулей с общим внешним интерфейсом (блоков выборки и декодирования), блока вычислений с плавающей запятой и кэш-памяти второго уровня.

Как утверждают в AMD, это было сделано для оптимизации конструкции и одновременно для снижения себестоимости. Поскольку в работающем многоядерном процессоре некоторые блоки часто остаются незадействованными, их можно сделать общими для нескольких «ядер». В результате процессор будет состоять из меньшего числа блоков и его физические размеры будут меньше. Это сделает его экономичнее, «прохладнее» и, разумеется, дешевле.

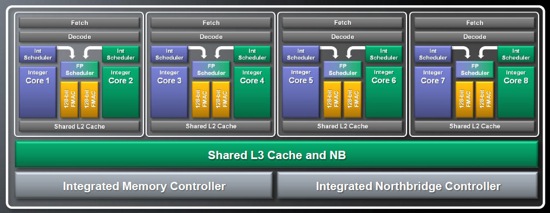

Конечно, такой процессор, строго говоря, не будет двухъядерным, ведь некоторые блоки у двух «недоядер» общие, поэтому применительно к ним в этой статье бы будем писать слово «ядра» в кавычках. При этом по производительности в реальных приложениях такой чип не будет уступать «настоящему» двухъядерному. Схему составленного из таких модулей восьмиядерного чипа можно увидеть на иллюстрации.

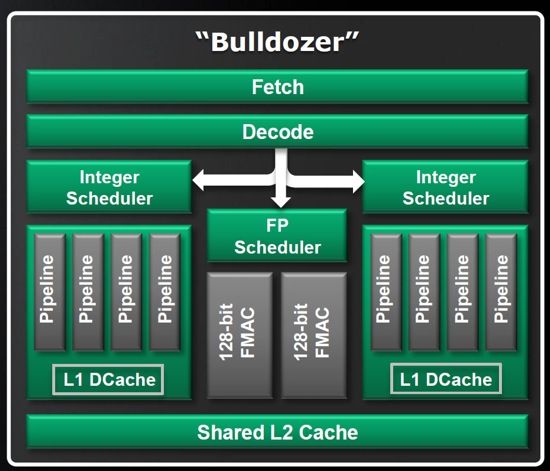

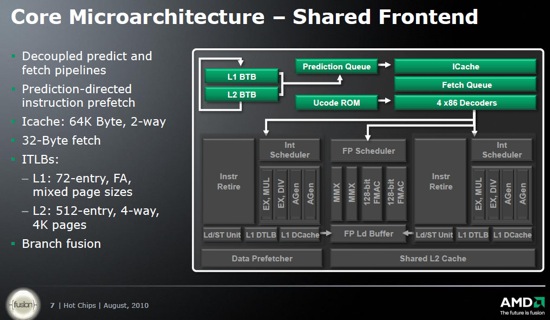

Блок выборки отвечает за отбор и передачу на декодирование следующей инструкции из кэш-памяти или оперативной памяти. Как упоминалось выше, этот блок является общим для двух «ядер» в каждом модуле. Кэш инструкций первого уровня, как неотъемлемая часть блока выборки, также общий для всего модуля, при этом у каждого «ядра» есть выделенный кэш данных L1.

Блок декодирования заведует преобразованием инструкций x86 в понятные процессору микроинструкции RISC. В каждом двухъядерном модуле четыре таких блока, причём пока в AMD не уточняют назначение каждого. Обычно по меньшей мере один блок работает со сложными инструкциями, дешифровка которых происходит за насколько тактов, в то время как простые инструкции дешифруются за один такт.

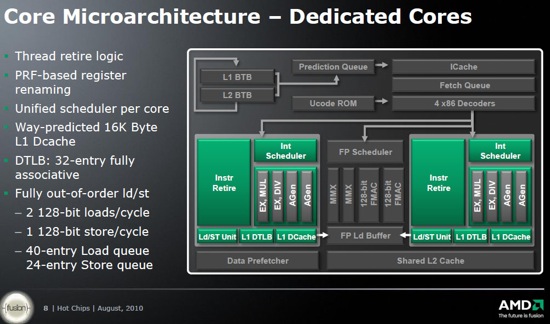

Расшифрованные инструкции отправляются на соответствующий планировщик, работающий с инструкциями для целочисленных вычислений или расчётов с плавающей запятой. Как и все прочие современные центральные процессоры, архитектура Bulldozer основана на внеочередном исполнении инструкций: для обеспечения равномерной загрузки исполнительных блоков в ней используются планировщики, сортирующие инструкции в произвольном порядке и отправляющие их на блоки, которые могут их исполнить.

Микроархитектурой Bulldozer предусмотрен лишь один блок вычислений с плавающей запятой на каждый двухъядерный модуль и два независимых «ядра», то есть, собственно, два блока целочисленных расчётов. В каждом «ядре» четыре исполнительных подблока: EX, MUL (выполняет любые целочисленные вычисления, за исключением деления), EX, DIV (выполняет любые целочисленные вычисления, за исключением умножения) и два AGen (блоки генерации адресов данных, используемых загружаемыми инструкциями). В каждом «ядре» также имеется блок загрузки и хранения (Ld/ST), отвечающий за выгрузку или загрузку в память данных, затребованных инструкцией. Выполненные целочисленные инструкции пересылаются на блок вывода, в котором они снова выстраиваются в правильном порядке.

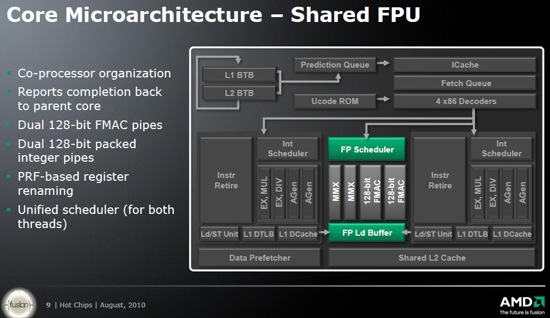

В блоке вычислений с плавающей запятой четыре подблока: два MMX (выполняет все основные вычисления с плавающей запятой x87, включая инструкции MMX/SSE) и два 128-битных блока FMAC (выполняет любые вычисления с плавающей запятой).

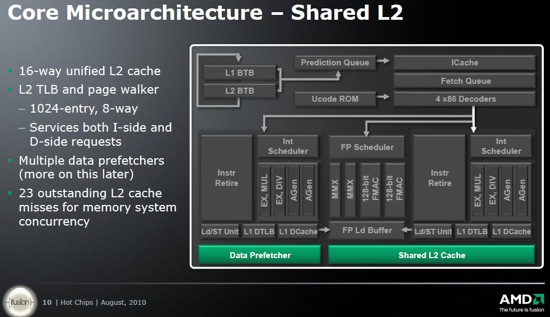

Архитектура Bulldozer предусматривает общую кэш-память второго уровня для двух «ядер». Кроме того, в чипах будет использоваться и кэш третьего уровня, общий для всех «ядер» и двухъядерных модулей.

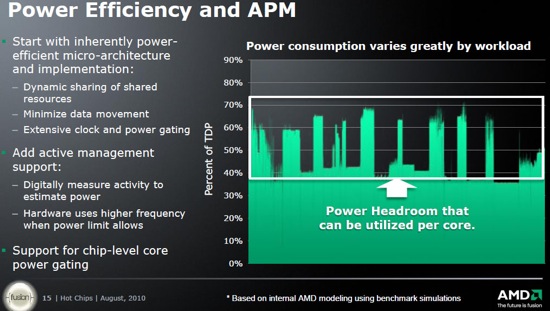

Новая микроархитектура предполагает несколько дополнений в системе управления питанием. В частности, в целях энергосбережения могут автоматически отключаться неиспользуемые блоки или целые «ядра».

В архитектуре Bulldozer будет также реализована технология автоматического разгона, аналогичная Turbo Boost, применяемой в процессорах Intel серий Core i7 и большей части Core i5. Напомним, что эта технология включается через BIOS и автоматически повышает тактовую частоту до заранее установленной величины при работе с ресурсоёмкими приложениями. Главное отличие этой системы от «нештатных» технологий разгона заключается в том, что она работает лишь при оптимальных настройках системы и при достаточно эффективном охлаждении, в противном случае Turbo Boost просто не включится.

Микроархитектура Bulldozer совместима со стандартными инструкциями x86 и поддерживает дополнительные наборы инструкций SSE4.1, SSE4.2, AVX, AES и LWP. В отличие от Intel Core, современные чипы AMD не работают с мультимедийными инструкциями SSE4.1/4.2, так что их поддержка в процессорах следующего поколения позволит существенно повысить их производительность при работе с цифровыми изображениями и видео. Проприетарный набор инструкций SSE4a в чипах AMD текущего поколения – это совершенно другой пакет, несовместимый с SSE4.1/4.2.

Набор векторных инструкций AVX (Advanced Vector Extensions) был разработан в Intel в качестве возможного набора мультимедийных инструкций SSE5 нового поколения, и он также будет использоваться в центральных процессорах этой компании следующего поколения на основе архитектуры Sandy Bridge. При этом в AMD решили дополнить этот набор двумя собственными расширениями XOP и FMA4, которые будут также реализованы в микроархитектуре Bulldozer.

Инструкции AES (Advanced Encryption Standard), уже используемые в современных чипах Intel (кроме младших Core i3), отвечают за поддержку алгоритмов шифрования, а LWP (Light Weight Profiling) позволяют одним программам отслеживать производительность других, что особенно важно при отладке софта.

Переход с заслуженной 64-битной архитектуры, впервые использованной семь лет назад в процессорах Athlon 64, на AMD Bulldozer запланирован на 2011 год. Как обычно, первыми чипами на базе новой микроархитектуры станут серверные процессоры, затем будут выпущены высокопроизводительные, и лишь после этого настанет пора массовых и бюджетных моделей.

Ожидается, что одновременно с выпуском новых «настольных» процессоров появится и новый разъём AM3+, причём системные платы для этих чипов будут совместимы с процессорами для AM3, но процессоры для AM3+ не будут поддерживаться на старых платах для AM3.

К оглавлению

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКЧитайте также

Золотой век ТВ ещё впереди Олег Нечай

Золотой век ТВ ещё впереди Олег Нечай Опубликовано 13 мая 2013 Вопреки распространённому мнению телевидение вовсе не умирает. И хотя социальные сети и новые технологические платформы буквально считают дни до его похорон, сегодня мы наблюдаем

Современные ЖК-мониторы Олег Нечай

Современные ЖК-мониторы Олег Нечай Опубликовано 05 августа 2011 года В течение последних десяти лет конструкция жидкокристаллических мониторов стремительно совершенствовалась, но ещё быстрее увеличивалась диагональ экрана: если в 2001 году

Четыре видеорегистратора Олег Нечай

Четыре видеорегистратора Олег Нечай Опубликовано 31 августа 2011 года Proline DVR-006 Один из самых популярных бюджетных видеорегистраторов, известный под самыми разными названиями, включая Proline DVR-006, или «Сова». Главная причина популярности —

Автомобильные видеорегистраторы Олег Нечай

Автомобильные видеорегистраторы Олег Нечай Опубликовано 31 августа 2011 года Не будем лукавить: чаще всего видеорегистраторы приобретаются с целью противостоять недобросовестным «продавцам полосатых палочек», пытающимся приписать водителям

Отстающий стремительный Олег Нечай

Отстающий стремительный Олег Нечай Опубликовано 05 апреля 2011 года Новый стандарт высокоскоростной беспроводной связи 4G, получивший индекс IEEE 802.16m, должен прийти на смену нынешнему поколению WiMAX IEEE 802.16e. Однако есть обоснованные сомнения в том, что

Ультрабук ещё не тот Олег Нечай

Ультрабук ещё не тот Олег Нечай Опубликовано 25 ноября 2011 года Летом 2011 года вице-президент корпорации Intel Мули Иден представил на международной выставке Computex 2011 новый класс портативных компьютеров — ультрабук. По его словам, это самое значительное

Пять проигрывателей Blu-ray Олег Нечай

Пять проигрывателей Blu-ray Олег Нечай Опубликовано 09 декабря 2011 года Panasonic DMP-BD75 Бюджетный проигрыватель Blu-ray c возможностью воспроизведения медиафайлов с внешних USB-накопителей. Ориентировочная розничная цена — 4200 рублей. Доступный

Новые «аймаки»: постоянство - признак зрелости Олег Нечай

Новые «аймаки»: постоянство - признак зрелости Олег Нечай Опубликовано 04 мая 2011 года Обновление линейки настольных моноблоков iMac не вызвало того ажиотажа, который обычно сопутствует выпуску других устройств под маркой Apple. И неудивительно: внешне

Новые мобильные процессоры. Часть 2 Олег Нечай

Новые мобильные процессоры. Часть 2 Олег Нечай Опубликовано 22 июня 2011 года Продолжение. Первая часть. Поскольку мобильные чипы, в отличие от «настольных», редко попадают в свободную продажу, в таблицах отсутствуют данные о розничных ценах. Intel

Современные струйные МФУ Олег Нечай

Современные струйные МФУ Олег Нечай Опубликовано 24 февраля 2011 года За последние пять лет огромную популярность завоевали так называемые «многофункциональные устройства», или MФУ. Это аппараты, объединяющие в себе принтер, сканер и, реже, факс, и

Новые гибридные процессоры AMD APU A-Series Олег Нечай

Новые гибридные процессоры AMD APU A-Series Олег Нечай Опубликовано 15 июня 2011 годаЗакрытая презентация A-Series для журналистов состоялась примерно за месяц до официальной, и к этому времени в продаже уже появились первые ноутбуки на базе новых чипов семейства Fusion. A-Series в AMD

Мыши для ноутбуков Олег Нечай

Мыши для ноутбуков Олег Нечай Опубликовано 08 ноября 2010 года Практически во всех портативных компьютерах есть встроенный манипулятор — сенсорная панель тачпад, или, как в ноутбуках ThinkPad, даже два — тачпад и трекпойнт. Однако если вы пользуетесь

Аккумуляторные батареи: от и до Олег Нечай

Аккумуляторные батареи: от и до Олег Нечай Опубликовано 08 декабря 2010 года В современных ноутбуках и прочих портативных электронных устройствах применяются два типа аккумуляторных батарей: ионно-литиевые (чаще всего обозначаются как Li-ion) и

Компьютеры-моноблоки — от и до Олег Нечай

Компьютеры-моноблоки — от и до Олег Нечай Опубликовано 16 марта 2011 года Однако на самом деле эта идея чуть раньше пришла в голову инженерам компании Commodore, которая занимала львиную долю рынка домашних компьютеров задолго до появления IBM PC. Commodore PET

Li-Fi: вайфай на лампочках Олег Нечай

Li-Fi: вайфай на лампочках Олег Нечай Опубликовано 16 мая 2012 года На выставке бытовой электроники CES 2012, проходившей в январе 2012 года в американской столице развлечений Лас-Вегасе, японская Casio продемонстрировала необычный фокус: один смартфон

Память завтрашнего дня Олег Нечай

Память завтрашнего дня Олег Нечай Опубликовано 18 апреля 2012 года Компьютерные накопители на основе микросхем флэш-памяти, получившие название SSD (Solid State Drive, то есть «твёрдотельный привод»), появились на массовым рынке всего лишь в середине