Схема для упрощения с использованием булевых функций

Схема для упрощения с использованием булевых функций

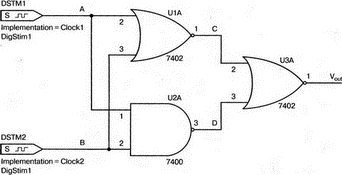

Цифровая схема, показанная на рис. 17.39, состоит из двух источников сигнала, одного элемента И-НЕ, и двух элементов ИЛИ-НЕ. Начните новый проект с именем mix и разместите компоненты, как показано на рисунке. В качестве учебного упражнения найдите таблицу истинности для схемы, затем на бумаге составьте булевые функции для схемы и упростите ее.

Рис. 17.39. Схема для упрощения с использованием булевых функций

Источники сигналов для нашего проекта должны быть такими же, как в предыдущем примере, в котором использовались компоненты DigStiml из библиотеки sourcstm. Один из таймеров (DSTIM1) имеет частоту f=1 кГц, а другой (DSTM2) — f=2 кГц. Оба таймера в начале моделирования обнулены. Используйте Place, Net Alias, чтобы маркировать узлы А, В, С, D и Vout. Подготовьте моделирование с именем mix1. Вызовите анализ переходных процессов на интервале в 2 мс с максимальным шагом в 2 мкс.

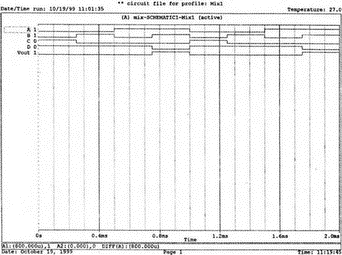

Проведите моделирование и получите в Probe все сигналы, как показано на рис. 17.40. Воспользуйтесь курсором, чтобы найти сигналы на выходах С, D, и Vout в различные моменты времени. Как следует из рисунка, при t=0,8 мс получаем А=1, В=1, С=0, D=0 и Vout=1. Убедитесь в соответствии этих результатов вашим таблицам истинности для каждой логической схемы. На рис. 17.41 показана часть выходного файла.

Рис. 17.40. Входные и выходные сигналы в схеме для упрощения

**** 09/06/99 20:30:17 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: Mix1

*Libraries:

* Local Libraries :

.STMLIB ".MIX.stl"

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib nom.lib

*Analysis directives:

.TRAN 0 2ms 0 2us

.PROBE

*Netlist File:

.INC "mix-SCHEMATIC1.net"

*Alias File:

**** INCLUDING mix-SCHEMATIC1.net ****

* source MIX

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND В IO_STM STIMULUS=Clock2

U_DSTM1 STIM(1,0) $G_DPWR $G_DGND A IO_STM STIMULUS=Clock1

X_U3A С D VOUT $G_DPWR$G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U2A А В D $G DPWR $G_DGND 7400 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U1A ABC $G_DPWR $G_DGND 7402 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

**** RESUMING mix-SCHEMATIC1-Mix1.sim.cir ****

.INC "mix-SСHEMATIC1.als"

**** INCLUDING mix-SCHEMATICl.als ****

.ALIASES

.END

* E:SPICEMIX.stl written on Mon Sep 06 20:26:10 1999

* by Stimulus Editor — Evaluation Version 9.0

;!Stimulus Get

;! Clock1 Digital Clock2 Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 4ms

;!AutoUniverse

;!XminRes 1ns

;!YminRes 1n

;!Ok

.STIMULUS Clock1 STIM (1, 1)

;! CLOCK 1kHz 0.5 0 0

+ +0s 0

+ +500us 1

+ Repeat Forever

+ +500us 0

+ +500us 1

+ EndRepeat

.STIMULUS Clock2 STIM (1, 1)

;! CLOCK 2kHz 0.5 0 0

+ +0s 0

+ +250us 1

+ Repeat Forever

+ +250us 0

+ +250us 1

+ EndRepeat

.STIMULUS Clock2 STIM(1, 1)

;! CLOCK 2kHz 0.5 0 0

+ +0s 0

+ +250us 1

+ Repeat Forever

+ +250us 0

+ +250us 1

+ EndRepeat

Рис. 17.41. Выходной файл схемы для упрощения

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

Схема data:URI

Схема data:URI Схема data:URI предоставляет способ для внедрения «непосредственно данных» точно так же, как если бы они были подключены через вызовы внешних файлов. Синтаксис у нее следующий:data:[<тип данных>][;base64],<данные>В случае простых изображений вам нужно указать

17.8.3. Пример поиска информации хоста с использованием унаследованных функций

17.8.3. Пример поиска информации хоста с использованием унаследованных функций Ниже приводится пример программы, использующей inet_aton(), inet_ntoa(), gethostbyname(), gethostbyaddr(). Она принимает единственный аргумент, который может быть либо именем хоста, либо IP-адресом в десятичном

Схема WS XML

Схема WS XML Синтаксис элементов, составляющих структуру WS-файла, в общем виде можно представить следующим образом:<element [attribute1="value1" [attribute2="value2" ... ]]> Содержимое (content)</element>Открывающий тег элемента состоит из следующих компонентов:? открывающей угловой скобки "<";?

Схема WSC XML

Схема WSC XML Ранее в главе 3 отмечалось, что объектная модель, которая используется при создании многозадачных сценариев (WS-файлов), была в основном позаимствована из схемы WSC XML, поэтому многие элементы WSC-файлов окажутся вам знакомыми.В листинге 10.1 приводится несколько

Схема ИЛИ-НЕ

Схема ИЛИ-НЕ В последнем примере главы 9 мы рассматривали логическую схему 7400: 2-входовую схему ИЛИ-НЕ. В качестве источников V1 и V2 были использованы источники напряжения типа PWL с выходным напряжением в виде последовательностей импульсов, представляющих уровни

Схема полусумматора

Схема полусумматора На самом деле нет необходимости использовать источник типа VPWL, чтобы обеспечить входные импульсы для цифровой схемы. Начните новый проект, использующий имя half. Библиотека Sourcestm содержит компонент DigStim1, условное обозначение которого показано на рис.

Схема документа

Схема документа Режим Схема документа является дополнительным режимом и работает с любым из рассмотренных выше. С его помощью можно быстро перемещаться между различными разделами, подразделами документа, а также просматривать структуру документа. Для применения этого

Совет 46. Передавайте алгоритмам объекты функций вместо функций

Совет 46. Передавайте алгоритмам объекты функций вместо функций Часто говорят, что повышение уровня абстракции языков высокого уровня приводит к снижению эффективности сгенерированного кода. Александр Степанов, изобретатель STL, однажды разработал небольшой комплекс

4.4.2.3. Создание геометрии с использованием MySQL-специфических функций

4.4.2.3. Создание геометрии с использованием MySQL-специфических функций MySQL обеспечивает набор полезных ненормативных функций для создания геометрии с WKB представлениями. Функции, описанные в этом разделе, MySQL-расширения спецификации OpenGIS. Результатами этих функций будут

12.3.5. Адаптеры функций для объектов-функций

12.3.5. Адаптеры функций для объектов-функций В стандартной библиотеке имеется также ряд адаптеров функций, предназначенных для специализации и расширения как унарных, так и бинарных объектов-функций. Адаптеры – это специальные классы, разбитые на следующие две

19.11.2. Вызов функций из файла функций

19.11.2. Вызов функций из файла функций Мы уже рассматривали, каким образом функции вызываются из командной строки. Эти типы функций обычно используются утилитами, создающими системные сообщения.А теперь воспользуемся снова описанной выше функцией, но в этом случае

21.1.3. Поток вывода булевых данных

21.1.3. Поток вывода булевых данных Команда tput включает незначительное количество булевых операторов. Название Значение chts Курсор трудно заметить hs Имеет строку

Урок 6.4. Расчеты с использованием функций и имен ячеек

Урок 6.4. Расчеты с использованием функций и имен ячеек Типы ссылок. Имена ячеек Ссылки на ячейки и диапазоны могут быть относительными и абсолютными. До сих пор в формулах использовались относительные ссылки, в которых обозначение ячейки состоит из буквы и цифры.

Практическая работа 46. Выполнение расчетов с использованием Мастера функций

Практическая работа 46. Выполнение расчетов с использованием Мастера функций Задание. Используйте функцию ОКРУГЛ для округления цен в прайс-листе из предыдущей практической работы (см. рис. 6.32). Округление необходимо, поскольку при пересчете может получиться результат с

Практическая работа 47. Расчеты с использованием логических функций

Практическая работа 47. Расчеты с использованием логических функций Задание. Рассчитать надбавку за стаж по следующей шкале: до трех лет – 0; от трех до 10 лет – 10 %, 10 и более лет – 20 %.Для решения задачи нужно сформулировать словесный вариант решения. Он может звучать