Схема полусумматора

Схема полусумматора

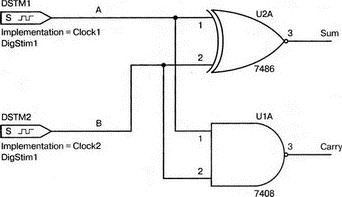

На самом деле нет необходимости использовать источник типа VPWL, чтобы обеспечить входные импульсы для цифровой схемы. Начните новый проект, использующий имя half. Библиотека Sourcestm содержит компонент DigStim1, условное обозначение которого показано на рис. 17.35, наряду с двумя другими компонентами из библиотеки eval: 2-входовой схемой исключающего ИЛИ 7486 и 2-входовой схемой И 7408. К выходу каждой из логических схем подключен короткий отрезок провода. Выходу компонента 7486, присвоен псевдоним «Sum», а выходу компонента 7408 — псевдоним «Carry».

Рис. 17.35. Схема полусумматора

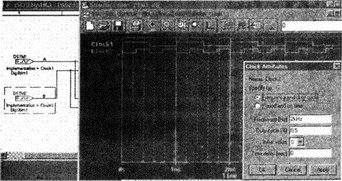

Выберите цифровую форму выходного напряжения под заголовком (А) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock1. Установите параметры: частота 1 кГц, коэффициент заполнения 0,5, начальное значение 1 и нулевое запаздывание.

Закройте редактор Stimulus и, модифицировав схему, сохраните изменения. Выберите теперь цифровую форму выходного напряжения под заголовком (В) с помощью Edit, PSpice Stimulus, New Stimulus, Digital, Clock, чтобы ввести цифровой таймер с именем Clock2. Он должен иметь параметры f=2 кГц, коэффициент заполнения 0,5, нулевое начальное значение и нулевое запаздывание. Редактор Stimulus отображает форму выходного сигнала для двух таймеров, как показано на рис. 17.36.

Рис. 17.36. Редактор Stimulus, показывает входные сигналы Clock1 и Clock2

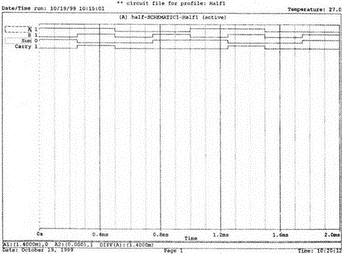

Подготовьте моделирование на PSpice с именем Half1. Выполните анализ переходных процессов на интервале в 2 мс с максимальным размером шага в 2 мкс. Проведите анализ и получите в Probe графики сигналов А, В, Sum, Carry (рис. 17.37). Если использовать курсор, то уровни этих сигналов будут показаны как единицы или нули. Как показано на рисунке, при t=1,4 мс получаются значения: А=1, В=1, Sum=0 и Carry=1. Часть выходного файла показана на рис. 17.38. При таком формировании входных сигналов не возникает необходимости в создании интерфейсов перехода от аналоговых к цифровым сигналам и обратно, так как используются только цифровые сигналы. В перечне элементов через U обозначаются компоненты с цифровым выходом, а через X — подсхемы.

Рис. 17.37. Входные и выходные сигналы для полусумматора

**** 10/18/99 21:28:59 *********** Evaluation PSpice (Nov 1998) **************

** circuit file for profile: Half1

*Libraries:

* Local Libraries :

.STMLIB ".HALF.stl"

* From [PSPICE NETLIST] section of pspiceev.ini file:

.lib "nom.lib"

* Analysis directives:

.TRAN 0 2ms 0 2us

.PROBE

*Netlist File:

.INC "half-SCHEMATIC1.net"

*Alias File:

**** INCLUDING half-SCHEMATIC1.net ****

* source HALF

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND В IO_STM STIMULUS=Clock2

U_DSTM1 STIM(1,0) $G_DPWR $G_DGND A IO_STM STIMULUS=Clock1

X_U2A А В SUM $G_DPWR $G_DGND 7486 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U1A А В CARRY $G_DPWR $G_DGND 7408 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

**** RESUMING half-schematic1-half1.sim.cir ****

.INC "half-SCHEMATIC1.als"

**** INCLUDING half-SCHEMATIC1.als ****

**** RESUMING half-schematicl-half1.sim.cir ****

.END

* E:SPICEHALF.stl written on Mon Sep 06 17:58:50 1999

* by Stimulus Editor — Evaluation Version 9.0 ;!Stimulus Get

;! Clock1 Digital Clock2 Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 4ms

;!AutoUniverse

;!XminRes 1ns

;!YminRes 1n

;!Ok

.STIMULUS Clock1 STIM (1, 1) ;! CLOCK 1kHz 0.5 1 0

+ +0s 1

+ +500us 0

+ Repeat Forever

+ +500us 1

+ +500us 0

+ EndRepeat

.STIMULUS Clock2 STIM (1, 1) ;! CLOCK 2kHz 0.5 0 0

+ +0s 0

+ +250us 1

+ Repeat Forever

+ +250us 0

+ +250us 1

+ EndRepeat

.STIMULUS Clock2 STIM (1, 1) ;! CLOCK 2kHz 0.5 0 0

+ +0s 0

+ +250us 1

+ Repeat Forever

+ +250us 0

+ +250us 1

+ EndRepeat

Рис. 17.38. Выходной файл для полусумматора

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

Схема уведомления

Схема уведомления Как получить уведомление о тайм-ауте? При использовании таймера задержки вы получаете уведомление просто посредством возвращения в состояние READY.При использовании периодически и однократных таймеров у вас появляется выбор:• послать

Схема data:URI

Схема data:URI Схема data:URI предоставляет способ для внедрения «непосредственно данных» точно так же, как если бы они были подключены через вызовы внешних файлов. Синтаксис у нее следующий:data:[<тип данных>][;base64],<данные>В случае простых изображений вам нужно указать

Схема WS XML

Схема WS XML Синтаксис элементов, составляющих структуру WS-файла, в общем виде можно представить следующим образом:<element [attribute1="value1" [attribute2="value2" ... ]]> Содержимое (content)</element>Открывающий тег элемента состоит из следующих компонентов:? открывающей угловой скобки "<";?

Схема WSC XML

Схема WSC XML Ранее в главе 3 отмечалось, что объектная модель, которая используется при создании многозадачных сценариев (WS-файлов), была в основном позаимствована из схемы WSC XML, поэтому многие элементы WSC-файлов окажутся вам знакомыми.В листинге 10.1 приводится несколько

5.1.1. Общая схема управления процессами

5.1.1. Общая схема управления процессами Каждый процесс может порождать полностью идентичный процесс с помощью fork(). Родительский процесс может дожидаться окончания выполнения всех своих процессов-потомков с помощью системного вызова wait. В любой момент времени процесс

1.1.1. Рекомендуемая схема разбиения диска

1.1.1. Рекомендуемая схема разбиения диска ? Раздел подкачки или свопинга (swapping) — используется виртуальной памятью. Иными словами, данные, не умещающиеся в оперативной памяти, перемещаются на жесткий диск. Например, у вас в данный момент свободно всего 8 Мбайт оперативной

Схема ИЛИ-НЕ

Схема ИЛИ-НЕ В последнем примере главы 9 мы рассматривали логическую схему 7400: 2-входовую схему ИЛИ-НЕ. В качестве источников V1 и V2 были использованы источники напряжения типа PWL с выходным напряжением в виде последовательностей импульсов, представляющих уровни

Схема водопровода и дренажной системы

Схема водопровода и дренажной системы Создание схем водопровода и дренажной системы (рис. 2.3) – необходимая составляющая предварительной подготовки проекта. Рис. 2.3. Схема дренажной системы выполнена в программе «КОМПАС-3D»На схеме указаны расположение и размеры

Схема системы полива

Схема системы полива Кроме схемы дренажа необходимо составить схему полива растений (рис. 2.4), расположенных на участке. Рис. 2.4. Схема системы полива создана в программе «КОМПАС-3D»На данном рисунке представлен подвод воды для полива растений на овальной клумбе. На схеме

Схема системы освещения

Схема системы освещения Очень важно продумать ночное освещение участка. Сделать грамотное освещение, учитывая все особенности участка, расположение объектов и дорожек, можно, если создавать план освещения в программе «КОМПАС-3D» (рис. 2.5). Рис. 2.5. Схема системы освещения,

Схема дорожек и площадок

Схема дорожек и площадок Расположив все объекты на участке, можно создать схему дорожек и площадок (рис. 2.6), что позволит продумать удобство эксплуатации участка. Рис. 2.6. Схема дорожек и площадок выполнена в программе «КОМПАС-3D»На данном рисунке представлен разбивочный

7.3. Схема производитель-потребитель

7.3. Схема производитель-потребитель Одна из классических задач на синхронизацию называется задачей производителя и потребителя. Она также известна как задача ограниченного буфера. Один или несколько производителей (потоков или процессов) создают данные, которые

Схема базы данных

Схема базы данных Для создания структуры базы данных рекомендуется не только подготовить список таблиц и полей, но и представить таблицы и поля в графическом виде. После этого вы не только сможете сказать, какие таблицы и поля доступны для вас, но и как они связаны друг с

Схема документа

Схема документа Режим Схема документа является дополнительным режимом и работает с любым из рассмотренных выше. С его помощью можно быстро перемещаться между различными разделами, подразделами документа, а также просматривать структуру документа. Для применения этого

Краткая схема сборки

Краткая схема сборки В принципе, вы можете собирать компьютер в той последовательности, в какой пожелаете. Мало того, в зависимости от размеров и конфигурации корпуса, а также размера материнской платы очередность операций может варьироваться. Иногда проще сначала