Страничный механизм

Страничный механизм

При реализации виртуальной памяти, основанной только на сегментации, весь сегмент целиком может либо присутствовать в оперативной памяти, либо отсутствовать (точнее, находиться во вторичной памяти или в исполняемом файле процесса). Поскольку размер сегмента может быть достаточно велик, одновременное выполнение нескольких больших процессов вызовет серьезную конкуренцию за ресурсы памяти, что в свою очередь приведет к интенсивному обмену данными между оперативной и вторичной памятью. К тому же обмен областями переменного размера, каковыми являются сегменты, достаточно сложен и, хотя фрагментация памяти при этом будет невелика, приведет к низкой эффективности ее использования, оставляя большое количество неиспользуемого пространства.

Страничный механизм обеспечивает гораздо большую гибкость. В этом случае все виртуальное адресное пространство (4 Гбайт для процессоров Intel) разделено на блоки одинакового размера, называемые страницами. Большинство процессоров Intel работает со страницами размером 4 Кбайт. Так же как и в случае сегментации, страница может либо присутствовать в оперативной памяти, либо находиться в области свопинга или исполняемом файле процесса. Основное преимущество такой схемы заключается в том, что система управления памятью оперирует областями достаточно малого размера для обеспечения эффективного распределения ресурсов памяти между процессами. Страничный механизм допускает, чтобы часть сегмента находилась в оперативной памяти, а часть отсутствовала. Это дает ядру возможность разместить в памяти только те страницы, которые в данное время используются процессом, тем самым значительно освобождая оперативную память. Еще одним преимуществом является то, что страницы сегмента могут располагаться в физической памяти в произвольном месте и порядке, что позволяет эффективно использовать свободное пространство[30].

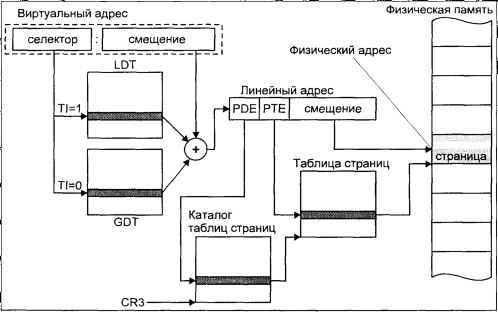

При использовании страничного механизма линейный адрес, полученный в результате сложения базового адреса сегмента и смещения также является логическим адресом, который дополнительно обрабатывается блоком страничной трансляции процессора. В этом случае линейный адрес рассматривается процессором как состоящий из трех частей, показанных на рис. 3.7.

Рис. 3.7. Трансляция адреса с использованием страничного механизма

Первое поле адреса, с 22 по 31 бит, указывает на элемент каталога таблиц страниц (Page Directory Entry, PDE). Каталог таблиц страниц имеет длину, равную одной странице, и содержит до 1024 указателей на таблицы страниц (page table). Таким образом, первое поле адресует определенную таблицу страниц. Второе поле, занимающее с 12 по 21 бит, указывает на элемент таблицы страниц (Page Table Entry, РТЕ). Таблицы страниц также имеют длину 4 Кбайт, а элементы таблицы адресуют в совокупности 1024 страниц. Другими словами, второе поле адресует определенную страницу. Наконец, смещение на странице определяется третьим полем, занимающим младшие 12 бит линейного адреса. Таким образом, с помощью одного каталога таблиц процесс может адресовать 1024?1024?4096 = 4 Гбайт физической памяти.

На рис. 3.7 показано, как блок страничной адресации процессора транслирует линейный адрес в физический. Процессор использует поле PDE адреса (старшие 10 бит) в качестве индекса в каталоге таблиц. Найденный элемент содержит адрес таблицы страниц. Второе поле линейного адреса, РТЕ, позволяет процессору выбрать нужный элемент таблицы, адресующий физическую страницу. Складывая адрес начала страницы со смещением, хранящимся в третьем поле, процессор получает 32-битный физический адрес.[31]

Каждый элемент таблицы страниц содержит несколько полей (табл. 3.2), описывающих различные характеристики страницы.

Таблица 3.2. Поля РТЕ

P Признак присутствия в оперативной памяти. Доступ к странице, отсутствующей в памяти (P=0) вызывает страничную ошибку, особую ситуацию, о чем процессор информирует ядро, которое обрабатывает ее соответствующим образом. R/W Права только на чтение страницы (R/W=0) или на чтение и запись (R/W=1). U/S Привилегии доступа. Если U/S = 0, только привилегированные задачи (ядро) имеют доступ к адресам страницы. В противном случае, доступ к странице имеют все задачи. Адрес Физический адрес начала страницы (адрес базы).Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

Старый механизм BH

Старый механизм BH Хотя старый интерфейс BH, к счастью, уже отсутствует в ядрах серии 2.6, тем не менее им пользовались очень долгое время — с первых версий ядра. Учитывая, что этому интерфейсу удалось продержаться очень долго, он, конечно, представляет собой историческую

Глава 15 Страничный кэш и обратная запись страниц

Глава 15 Страничный кэш и обратная запись страниц В ядре операционной системы Linux реализован один главный дисковый кэш, который называется страничным (page cache). Назначение этого кэша — минимизировать количество дисковых операций ввода-вывода путем хранения в памяти тех

Страничный кэш

Страничный кэш Как следует из названия, страничный кэш (page cache) — это кэш страниц; памяти. Соответствующие страницы памяти получаются в результате чтения и записи обычных файлов на файловых системах, специальных файлов блочных устройств и файлов, отображаемых в память.

8.9.3 Механизм RIP версии 1

8.9.3 Механизм RIP версии 1 Рассмотрим формальные этапы маршрутизации в RIP версии 1. Предположим, что в таблице маршрутизации уже есть сведения о нескольких расстояниях. Затем, когда от соседа прибывает информация об изменениях, маршрутизатор перепроверяет свою таблицу и

1.2.3. Поисковый механизм

1.2.3. Поисковый механизм Начиная выполнять поиск с помощью Яндекса, мы может в явном виде указать, в какой базе (коллекции документов, типе документов) следует выполнять поиск. Если мы не указываем этого, то на основе анализа запроса Яндекс самостоятельно делает допущение о

Механизм UAC

Механизм UAC Существует несколько возможностей настройки работы механизма UAC операционной системы Windows Vista. Все они основаны на использовании параметров REG_DWORD-типа ветви реестра HKEY_LOCAL_MACHINESOFTWAREMicrosoftWindowsCurrentVersionPoliciesSystem.• ConsentPromptBehaviorAdmin – позволяет определить режим

Механизм предвыборки

Механизм предвыборки Механизм предвыборки позволяет ускорить загрузку часто используемых при работе пользователя в операционной системе программ. Это достигается предварительным помещением в оперативную память данных таких программ. При этом механизм предвыборки

13-я комната: Защитный механизм

13-я комната: Защитный механизм Защитный механизмАвтор: Владимир ГуриевОпубликовано в журнале "Компьютерра" N25-26 от 08 июля 2008 годаЯпишу эту колонку за несколько часов до запуска Большого адронного коллайдера.Или мы найдем бозон Хиггса, или бозон Хиггса найдет нас. Не

Механизм сборки мусора

Механизм сборки мусора Сборщик мусора (garbage collector) - это функция исполнительной системы (runtime system) языка программирования. Сборщик мусора выполняет обнаружение и утилизацию недостижимых объектов, не нуждаясь в управлении приложением, хотя приложение может иметь в своем

Механизм освобождения

Механизм освобождения Другой важной процедурой класса MEMORY является dispose (не путайте с тезкой Pascal, которая освобождает память). Она связана с важной практической проблемой, иногда называемой финалом или окончательным завершением (finalization). Если сборщик мусора утилизирует

Механизм сборки мусора

Механизм сборки мусора Приведем схему алгоритма, используемого сборщиком мусора.Решение представляет собой не единственный алгоритм, а основано на комбинации основных алгоритмов, часть из которых используется совместно, часть - независимо друг от друга. Каждая

Механизм исключений

Механизм исключений Из предшествующего анализа следует механизм исключений, наилучшим образом соответствующий ОО-подходу и идеям Проектирования по Контракту.Для обеспечения основных свойств введем в язык два новых ключевых слова. Для случаев, в которых необходим

Механизм решения

Механизм решения И снова запись механизма решения напрямую вытекает из анализа поставленной проблемы. Введем новую форму присваивания, назвав ее попыткой присваивания (assignment attempt):target ?= sourceЗнак вопроса указывает на предварительный характер операции. Пусть сущность target

Статический механизм

Статический механизм Устранить последнее неясности в понимании закрепленного объявления поможет следующее замечание: это чисто статический механизм, не предполагающий никаких изменений объектов в период выполнения. Все ограничения могут быть проверены в период