Микросхема ИЛИ-НЕ 7402

Микросхема ИЛИ-НЕ 7402

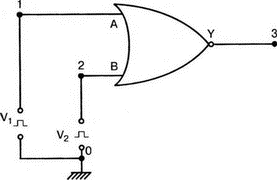

Микросхема, содержащая единственную логическую схему ИЛИ-НЕ, показана на рис. 9.26. Напряжения на двух входах А и В показаны как последовательности импульсов различной длительности с амплитудой 1 В. Схема ИЛИ-НЕ вводится с помощью вызова подпрограммы (командой X) в которой узлы 1, 2 и 3 относятся ко входам А и В и выходу Y соответственно. При вызове подпрограммы устройство называется 7402. Окончательный вид входного файла:

Digital Circuit Using NOR gate

VCC 4 0 5V

X 1 2 3 7402

V1 1 0 PWL(Сs 0V 0.1ms 1V 1s 1V 1.0001s 0V

+2s 0V 2.0001s 1V 3s 1V 3.0001s 0V 4s 0V 4.0001s 1V 5s

+1V)

V2 2 С PWL(0s 0V 1.5s 0V 1,50001s 1V 2.5s 1V 2.50001s 0V

+3.5s 0V 3.50001s 1V 3.7s 1V 3.70001s 0V 5s 0V)

R 4 3 100k

.lib eval.lib

.tran 0.01ms 5s

.probe

.end

Рис. 9.26. Схема ИЛИ-НЕ с двумя входами

В приложении Е можно найти описание модели

.subckt 7402 А В Y …

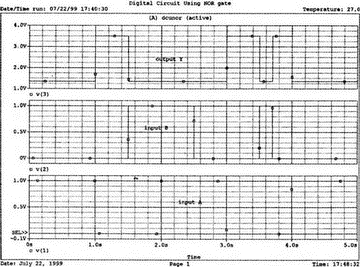

в котором показана вся подпрограмма. Ее не нужно включать во входной файл, достаточно ссылки на библиотеку EVAL.LIB, которая содержит всю необходимую информацию. В Probe получите напряжения v(1) и v(2), отображающие входные сигналы A и B, и напряжение v(3), отображающее выходной сигнал Y. Ваши результаты должны соответствовать приведенным на рис. 9.27, который показывает сигналы в виде трех отдельных графиков. В совокупности они просто представляют собой диаграмму синхронизации для нашей логической схемы.

Рис. 9.27. Входное и выходное напряжения в схеме ИЛИ-НЕ

В распечатке выходного файла (рис. 9.28) показана только часть общего файла. Распечатка параметров модели была опущена, чтобы сэкономить место. Обратите внимание, что аналого-цифровые команды реализуются в форме вызова подпрограмм, автоматически генерируемых подпрограммой 7402. Они имеются для каждого из трех узлов ИЛИ-НЕ. Команды для источника питания цифровой схемы также генерируются автоматически. Обратите внимание на листинг $G_DPWR=5 V наряду с другими узловыми напряжениями.

Digital Circuit Using NOR gate

VCC 4 0 5 V X 1 2 3 7402

V1 1 0 PWL(0s 0V 0.1ms 1V 1s 1V 1.0001s 0V

+2s 0V 2.0001s 1V 3s 1V 3,0001s 0V 4s 0V 4.0001s 1V 5s 1V)

V2 2 0 PWL (0s 0V 1.5s 0V 1.50001s 1V 2.5s 1V 2.50001s 0V

+3.5s 0V 3,50001s 1V 3.7s 1V 3.70001s 0V 5s 0V)

R 4 3 100k

.opt nopage

.lib eval.lib

.trail 0.01ms 5s

.probe

.end

**** Generated AtoD and DtoA Interfaces ****

* Analog/Digital interface for node 3

* Moving X.U1:OUT1 from analog node 3 to new digital node 3$DtoA

X$3_DtoA1

+ 3$DtoA

+ 3

+ $G DPWR

+ $G_DGND

+ DtoA_STD

+ PARAMS: DRVH= 96.4 DRVL= 104 CAPACITANCE= 0

*

* Analog/Digital interface for node 1

* Moving X.U1:IN1 from analog node 1 to new digital node 1$AtoD

X$1_AtoD1

+ 1

+ 1$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* * Analog/Digital interface for node 2

* Moving X.U1:IN2 from analog node 2 to new digital node 2$AtoD

X$2_AtoD1

+ 2

+ 2$AtoD

+ $G_DPWR

+ $G_DGND

+ AtoD_STD

+ PARAMS: CAPACITANCE= 0

* Analog/Digital interface power supply subcircuits X$DIGIFPWR 0 DIGIFPWR

**** Diode MODEL PARAMETERS

**** BJT MODEL PARAMETERS

**** Digital Input MODEL PARAMETERS

**** Digital Output MODEL PARAMETERS

**** Digital Gate MODEL PARAMETERS

**** Digital IO MODEL PARAMETERS

**** INITIAL TRANSIENT SOLUTION TEMPERATURE = 27.000 DEG С

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

( 1) 0.0000 ( 2) 0.0000 ( 3) 3.5028 ( 4) 5.0000

($G_DGND) 0.0000 ($G_DPWR) 5.0000

(X$1_AtoD1.1) .0915 (X$1_AtoD1.2) .0457

(X$1_AtoD1.3) .8277 (X$2_AtoD1.1) .0915

(X$2_AtoD1.2) .0457 (X$2_AtoD1.3) .8277

DGTL NODE : STATE DGTL NODE : STATE DGTL NODE : STATE DGTL NODE : STATE

( 2$AtoD) : 0 ( 3$DtoA) : 1 ( 1$AtoD) : 0

Рис. 9.28. Выходной файл при анализе схемы ИЛИ-НЕ

В качестве упражнения измените сигналы синхронизации для двух входов так, чтобы они создали области совпадения, отличные от уже использованных, и выполните моделирование снова. Опираясь на ваши теоретические сведения о работе схемы ИЛИ-НЕ, проверьте результаты.

В заключение замените схему 7402 на логическую схему И 7408 и проведите аналогичный анализ.

Более 800 000 книг и аудиокниг! 📚

Получи 2 месяца Литрес Подписки в подарок и наслаждайся неограниченным чтением

ПОЛУЧИТЬ ПОДАРОКДанный текст является ознакомительным фрагментом.

Читайте также

Кивино гнездо: Татуировка-микросхема Киви Берд

Кивино гнездо: Татуировка-микросхема Киви Берд Опубликовано 16 августа 2011 года Электронная «татуировка» В августовском номере известного научного журнала Science была представлена новая микроэлектронная технология, получившая название